艾目前,随着一些便携式电子系统,如笔记本电脑、PDA、手机等的广泛应用,集成电路的功耗也被提到与面积和速度同等重要的位置。如果仍使用传统的技术,就可能负担相当重量的电池,或者电池的使用时间相当短;而随着集成电路集成度的提高,在设计时若不考虑功耗问题,可能会使电路某些部分因功耗过大引起温度过高,导致系统工作不稳定或失效;功耗过大也会给封装带来很大困难,因此本文分别对CMOS集成电路的功耗来源和低功耗的设计方法及设计工具等进行了介绍。

1.CMOS电路功耗的来源

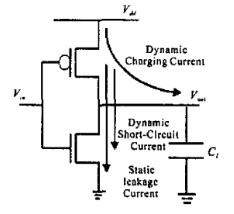

CMOS电路中有两种主要的功耗来源:静态功耗和动态功耗。其中,动态功耗包括短路电流引起的功耗(称为直流开关功耗或短路功耗,发生在跃变过程中双管同时导通引起的瞬态电流而形成的功耗)和负载电容的功耗(称为交流开关功耗,由对负载电容充放电电流引起的功耗);静态功耗主要是由漏电流引起的功耗(图1)。

图1CMOS集成电路功耗

1.1动态功耗

(1)交流开关功耗

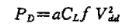

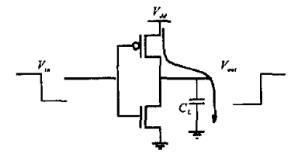

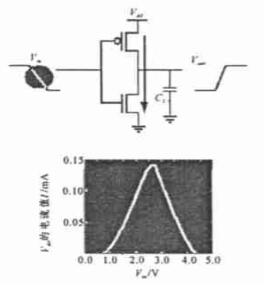

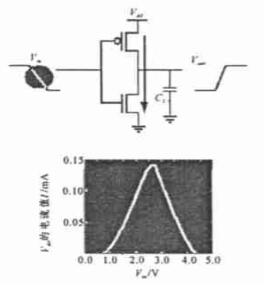

当反相器的输入为理想阶跃波时,对纯电容负载CL充放电所消耗的功率为交流开关功耗(图2)。CMOS反相器的平均动态功耗为:

式中,a为开关系数,即每个时钟周期中发生状态变化器件的个数,CL为负载电容,f为电路的工作频率,Vdd为电路的电源电压值。

图2CMOS电路的交流开关功耗

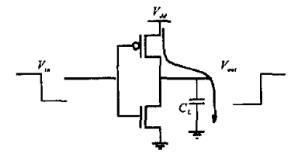

(2)直流开关功耗

当反相器输入为非理想阶跃波时,在输入波上升沿或下降沿瞬间,存在Р管和N管同时导通的区域,由此引起的功耗称直流开关功耗或短路功耗。其值为:

式中,Vdd为电路的电源电压值,Isr为短路电流值(见图3)

图3CMOS电路的直流开关功耗

1.2静态功耗

从理论上讲,CMOS电路在稳定状态下没有从电源到地的直接路径,所以没有静态功耗。然而,在实际情况下,扩散区和衬底之间的PN结上总存在反向漏电流,该漏电流与扩散结浓度和面积有关,从而造成一定的静态功耗(参见图4),其值可表示为:

式中,Vdd为电路的电源电压值,Ileakaze为漏电流的值(见图5)。

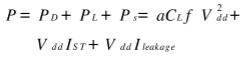

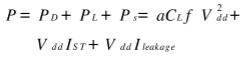

通过以上讨论,可以得到电路的总功耗为:

式中,占主要地位的是PD,它主要取决于三个参数:负载电容、时钟频率和电源电压。随着CMOS集成电路尺寸的减小,栅电容和电源电压也相应减小,当门数固定、时钟频率提高时,由于功耗近似正比于频率和负载电容的一次方,而正比于电源电压的二次方,所以整个电路功耗将减小。

图4CMOS电路的静态功耗

图5CMOS电路的漏电流

2.低功耗设计方法

2.1工艺调整的影响

随着工艺的发展,沟道长度不断减小,金属层不断增加,对低功耗设计带来一定的影响。作为电路设计者,不可能去改变工艺上的参数,但是对这些工艺的了解有助于设计。

(1)Vr的优化

随着工艺的进步和频率的不断提高,器件特征尺寸随之减小,氧化层的厚度也相应变薄,器件所能承受的电压降低,使电源电压减小,从而降低了功耗。由于电源电压减小,阈值电压Vr必须从先前的0.7~1.0V下降到0.~0.3V。但是,随着Vr的减小,漏电流所产生的功耗在总功耗中所占的比例就有可能上升。

(2)工艺尺寸的减小

器件工艺尺寸的不断减小对功耗的降低和电路速度的提高有着重要的影响。其中主要的一点是整个电容的减少,这将在一定程度上减少电路的功耗和延迟。栅电容和连线电容一般可以用下式表示:

式中,W为宽度,L为长度,tox为氧化层厚度,Eαr为氧化层介电常数。

但是,金属互连线的厚度几乎没有随着工艺尺寸缩小而减小,所以金属层和衬底的侧壁电容变化不大。因此,电容的减小不如我们想象的那么明显。

随着器件工艺尺寸的减小,降低了电路的电源电压,前面已分析过电路的功耗与Vdd近似成正比,所以功耗有明显的下降。

(3)工艺制造的进步

在现在先进的工艺制造中,一些新技术的采用,例如金属层的增加、允许通孔层叠等,都对降低功耗有一定的影响。

对于两层金属的工艺,在布线时,由于上层金属一般用于cell和cell之间的全局连接,所以一些cell内部的信号线常用多晶硅连接。如果有两层或更多的金属层,就可以利用高层的金属来进行cell内部的信号连线。对于各不同层的金属来说,它们的单位电容值是随层次的增高而降低的。因此,运用多层金属布线可以相对地减少电路的功耗。

通孔和通孔之间的距离在一定程度上决定了电路面积的大小,如果允许通孔的层叠,电路面积将有可能减少,同样也减少了cell内部和全局布线的金属线的长度。但是,相互间连线的耦合电容将有可能增加,就可能抵消先前的功耗降低。

2.2设计方法

(1)总线

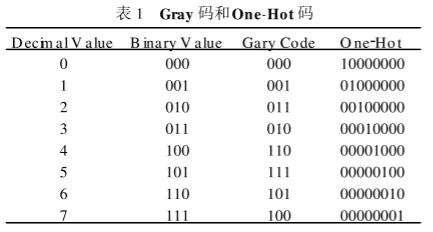

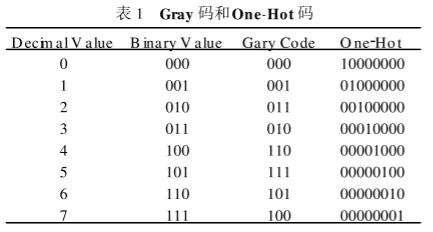

对某些电路的设计来说,它会包含相当数量的总线。由于总线会带来大负载、长连线、大电阻等效应,所以,总线的功耗要占整个芯片总功耗的15%~20%。为了降低这一部分功耗,可以利用一些特定的编码来减少信号的变化数,以降低由数据传输而造成的功耗。一般可采用One-Hot(在一个二进制数中,只允许一个数位不同于其它各数位的值)或Gray码(任何两个连续的数字,其对应的二进制码只有一个位的数值不同,其余位数值均相同)在访问相邻的两个地址的内容时,其跳变次数比较少,这样可以避免额外功耗的产生。(见表1)

(2)门控时钟

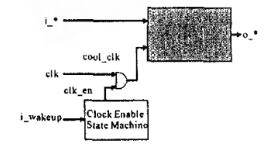

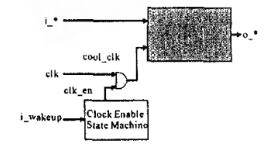

对于时序逻辑电路,时钟树消耗的功耗约为整个芯片功耗的15%~45%。为了减少这一部分功耗,可以采用门控时钟(clockgating),使一些暂时不工作的器件处于非触发状态,当需要这些器件工作时,可以用使能信号触发它们,通过这一方法可以减少不必要的功耗。

图6门控时钟

需要注意的是,门控时钟信号应置于相对较高的层次,而不是针对某个特定的触发器。如果这样的话,会造成不必要的clockskew(时钟之间的时间差,见图7)

图7时钟之间的时间差

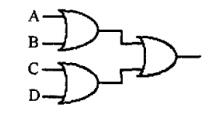

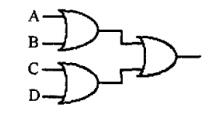

(3)闪变信号

对于含有组合逻辑的电路来说,它的闪变信号(glitch)功耗将占整个芯片功耗的15%~20%。在静态逻辑门电路中,输出口或器件内部接点的信号会在正确的逻辑值稳定之前变化,这种不必要的信号变化将造成额外的功耗(见图8)。一个两输入与门,输入信号分别由01→10,假定器件的门延时为0,则输出端恒为0。由于输入端信号到达的时间不同,就会出现多余的信号变化,信号的变化使a端开关系数值增加,功耗随之增大。

闪变信号的产生与路径的长度有一定的关系。一般来说,路径越长,越易产生闪变信号,原因之一是,不同的信号路径长度会造成信号到达时间的不同。因此在设计时,应尽量避免长线的逻辑组合,或调整其结构,采用平衡树结构(见图9)。此外,也可以通过其它方法来平衡电路的延迟,例如选择不同驱动能力的逻辑器件,或者在电路中插入buffer。但一般只有通路中的器件开关频率较高时,才用这种方法来改善功耗问题。

图8闪变信号

图9平衡树结构

(4)睡眠模式

睡眠模式(sleepmode)是一种可以用来降低功耗的可选方式。整个系统的动作状态处于被监控的状态,如果系统或电路在某段预设的时间段内处于闲置状态,那么整个系统或电路将自动关闭。但是其输入还是处于响应状态,一旦有任何输入信号被触发,整个系统或电路将被重新激活,回到正常的工作状态,这样可以降低相应的功耗。这种模式对需处于睡眠状态时间较长的器件比较有利,因为从睡眠状态到正常工作状态的时间有时需要几微秒,甚至几毫秒,而且系统或电路在进入睡眠状态和恢复到正常工作状态都会有额外的功耗。

3.低功耗设计工具

现在有许多低功耗设计的EDA工具。根据工具所使用的不同阶段,可以把它们分为四类:晶体管级、门级、RTL级和行为级。

3.1晶体管级

晶体管级的功耗分析工具是以晶体管为基本器件来估算电路的功耗,这类工具比较成熟、精确、易懂。但此时已处于设计的后期阶段,没法对设计作大量的修改。代表性的工具有Synopsys的Power-MillSPCE、Mentor的MarchPA等。

3.2门级

门级的功耗分析工具是以逻辑门为基本器件来估算电路的功耗。尽管这类工具不如晶体管级功耗分析工具精确,但是由逻辑门表示的电路比由晶体管表示的电路更易懂。代表性的工具有Synopsys的PowerCompiler,它可以重新优化设计,满足功耗的要求。

3.3RIL级

RTL级的功耗分析工具是以RTL器件为基本器件来估算电路的功耗。由于它处于设计的前端,所以这类工具对整个电路设计的功耗特性有着重要的影响。它们的速度较前两者快,容量较前两者大,但精确度相对较低。此外,这一类工具可有效地估算由门控时钟引起的功耗。

3.4行为级

目前行为级的功耗分析工具还处于研发阶段。

总结

以上就是CMOS集成电路低功耗的设计方法介绍了。CMOS集成电路可在较广泛的电源电压范围内工作,便于与其他电路接口;并且速度快,门延迟时间达纳秒级;在模拟电路中应用,其性能比NMOS电路好;与NMOS电路相比,集成度稍低。

〈烜芯微/XXW〉专业制造二极管,三极管,MOS管,桥堆等,20年,工厂直销省20%,上万家电路电器生产企业选用,专业的工程师帮您稳定好每一批产品,如果您有遇到什么需要帮助解决的,可以直接联系下方的联系号码或加QQ/微信,由我们的销售经理给您精准的报价以及产品介绍

联系号码:18923864027(同微信)

QQ:709211280