推挽电路(push-pull)就是两个不同极性晶体管间连接的输出电路。它采用两个参数相同的功率BJT管或MOSFET管,以推挽方式存在于电路中,各负责正负半周的波形放大任务。电路工作时,两只对称的功率开关管每次只有一个导通,所以导通损耗小,效率高。推挽输出既可以向负载灌电流,也可以从负载抽取电流。

在电路设计中,推挽输出是一种很常用的输出模式,具有很多优点,如更低的损耗、更安全的输出等。“推挽”之意,即为当一个管子推出去时,另一个管子拉回来。输入不同,交替导通。例如,当输入信号为高电平的时候,上面的管子导通,下面的管子截止,输出信号为高电平;当输入信号为低电平的时候,上面的管子截止,下面的管子导通,输出信号为低电平。

推挽结构一般是指两个三极管分别受两互补信号的控制,总是在一个三极管导通的时候另一个截止。要实现线与需要用OC(open collector)门电路。推挽电路适用于低电压大电流的场合,广泛应用于功放电路和开关电源中。

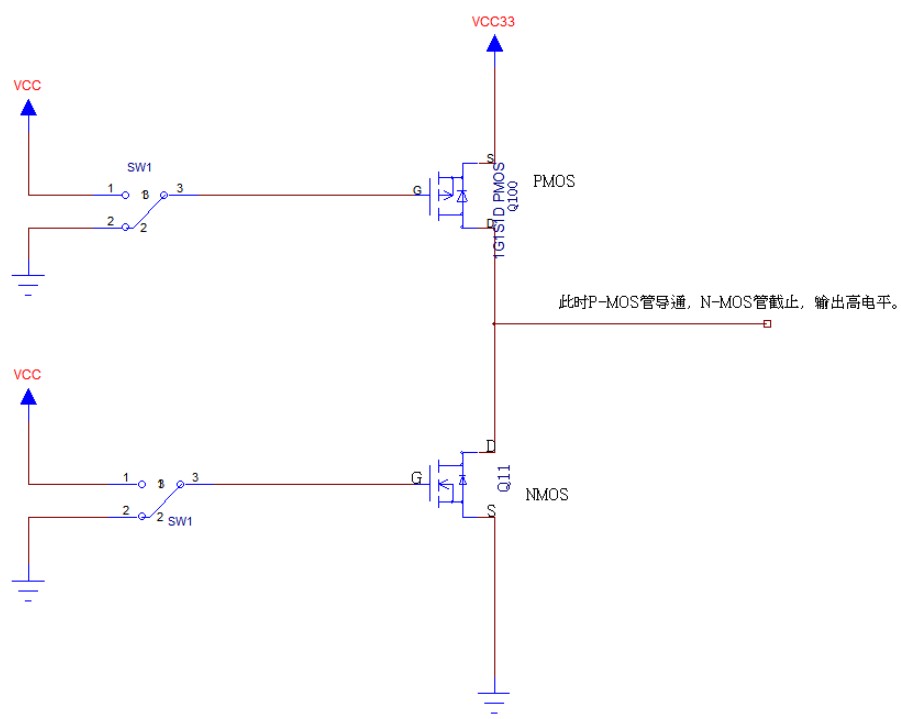

推挽输出高电平

在推挽输出模式下,一个晶体管用于提供高电平输出,而另一个晶体管则用于提供低电平输出。当内部输出为1电平时,上边的晶体管(如MOS管)导通,同时下边的晶体管截止,这时输出高电平。

推挽输出的高电平电压值取决于电路设计和应用环境。在某些情况下,推挽输出的高电平可能接近电源电压,例如3.3伏或5伏。然而,实际的电压值可能会受到多种因素的影响,包括晶体管的导通压降、电源电压的稳定性以及负载的阻抗等。

在推挽输出模式下,P-MOS管和N-MOS管同时工作,通过对两个MOS管的导通控制,实现控制输出高低电平,如图所示:

因此,要了解推挽输出的具体高电平值,需要参考相关的电路设计文档或应用手册,或者通过实际测量来确定。此外,推挽输出通常与数字信号相配合,其中逻辑高电平(通常为Vcc)与一个晶体管连接,逻辑低电平(通常为地)与另一个晶体管连接。

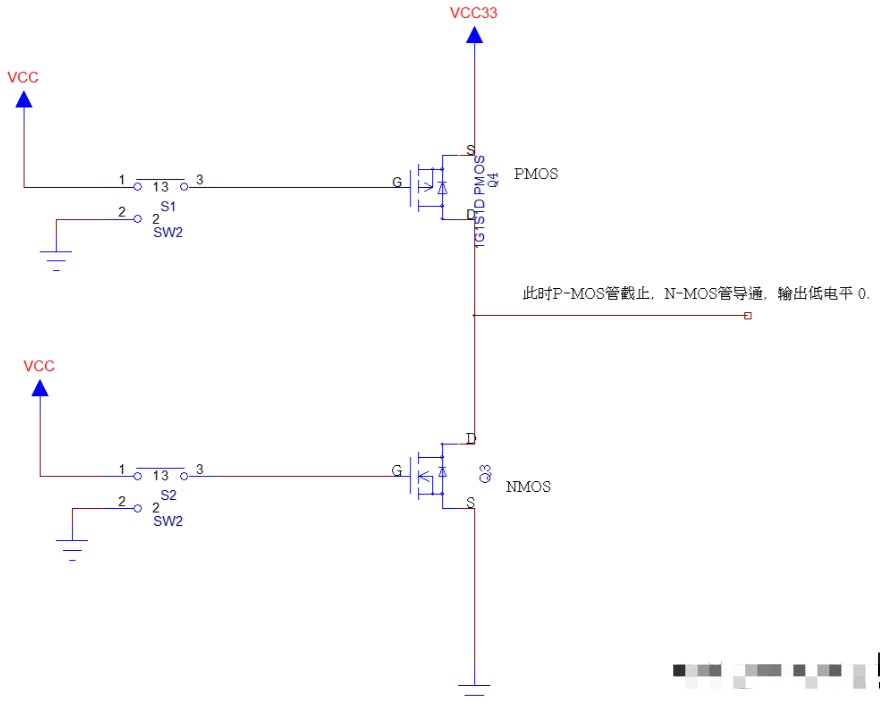

推挽输出低电平

在推挽输出模式下,GPIO口是可以直接输出高低电平的,不需要额外的上来或下拉辅助电路,如图所示:

推挽输出电路中的低电平通常是由另一个晶体管(如MOS管)在截止状态时提供的。在这种情况下,输出端会被拉向低电平,通常是地(GND)或接近地的电压。

当推挽输出电路中的内部信号为0时,控制低电平输出的晶体管会导通,而控制高电平输出的晶体管会截止。这样,电流会通过导通的晶体管流向地,从而将输出端拉至低电平。

低电平的电压值通常接近地电平(0V),但具体的电压值也会受到多种因素的影响,如晶体管的截止电压、电源电压的稳定性以及负载的阻抗等。

推挽输出电路中的低电平并不是由电源直接提供的,而是通过晶体管的截止状态来实现的。因此,低电平的电压值可能会受到晶体管性能和电路设计的影响。

〈烜芯微/XXW〉专业制造二极管,三极管,MOS管,桥堆等,20年,工厂直销省20%,上万家电路电器生产企业选用,专业的工程师帮您稳定好每一批产品,如果您有遇到什么需要帮助解决的,可以直接联系下方的联系号码或加QQ/微信,由我们的销售经理给您精准的报价以及产品介绍

联系号码:18923864027(同微信)

QQ:709211280