本文分析了第二代开关电流存储单元存在的问题,提出了改进方法,并设计了延迟线电路。此电路可以精确地对信号进行采样并延迟任意时钟周期。解决了第二代开关电流存储单元产生的误差,利用此电路可以方便地构造各种离散时间系统函数。

1、第二代开关电流存储单元分析

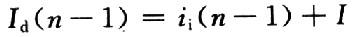

第二代开关电流存储单元,在φ1(n-1)相,S1,S2闭合,S3断开,晶体管M连成二极管形式,输入电流ii与偏置电流I之和给栅源极间电容C充电。随着充电的进行,栅极电压vgs达到使M能维持整个输入电流的电平,栅极充电电流减至零,达到稳态,此时M的漏极电流为:

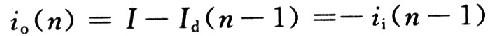

在φ2(n)相,S1,S2断开,S3闭合,此时输出端电流为:

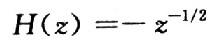

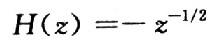

Z域传输函数为:

综上可看出,晶体管M既作为输入存储管又作为输出管,输出电流i0仅在φ2相期间获得。

2、延迟线

从结果来看,由于时钟馈通误差和传输误差的存在,第二代开关电流存储单元(以下简称基本存储单元)输出波形严重失真,尤其是级联后的电路失真更加严重,无法应用到实际中,所以,设计延迟线电路。

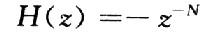

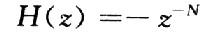

电路原理如下:电路是一个由N+1个并联存储单元组成的阵列,且由时钟序列控制。在时钟的φ0。相,存储单元M0接收输入信号,而单元M1提供其输出。类似的,在φ1相,单元M1接收输入信号,单元M2提供其输出。这个过程一直持续到单元MN接收其输入信号,单元M0提供其输出信号为止,然后重复循环。显然,每个单元都是在其下一个输入之前一个周期,即在其前一个输出相N个周期(NT)之后,提供输出信号。如取N=1,则延迟线是一个反相单位延迟单元,或连续输入信号时,它是一个采样保持电路,此时,延迟线电路和基本存储单元相同。请注意,对于循环的N-1个时钟相,每个存储单元既不接收信号也不提供信号。在这些时刻,存储晶体管上的漏电压值变化到迫使每个偏置电流和保持在其有关存储晶体管中的电流之间匹配。给出Z域传输函数为:

用基本存储单元级联延迟N个周期,则需要2N个基本存储单元级联,并且电路的时钟馈通误差和传输误差会随着N的增加越来越严重,到最后原信号将淹没在误差信号中。延迟线电路若要实现信号延迟N个时钟周期,则需要N+1个并联存储单元组成,并且需要N+1种时序。由于这种电路结构不需要级联,所以并不会像基本存储单元级联那样使得时钟馈通误差和传输误差越来越大。但是时钟馈通误差和传输误差仍然存在,以下给出解决办法。

3、时钟馈通误差及传输误差的改善

3.1 时钟馈通误差的改善

改善时钟馈通误差可采用S2I电路。它的工作原理为:在φ1a相,Mf的栅极与基准电压Vref相连,此时Mf为Mc提供偏置电流JoMc中存储的电流为ic=I+ii。当φ1b由高电平跳变为低电平时,由于时钟馈通效应等因素造成Mc单元存储的电流中含有一个电流误差值,假设它为△ii,则Mc中存储的电流为ic=J+ii+△ii。在φ1b相期间,细存储管Mf对误差电流进行取样,由于输入电流仍然保持着输入状态,所以Mf中存储的电流为If=J+△ii。当φ1b由高电平跳变为低电平时,考虑到△ii

3.2 传输误差的改善

传输误差产生的原因是当电路级联时,因为传输的是电流信号,要想信号完全传输到下一级,必须做到输出阻抗无穷大,但在实际中是不可能实现的,只能尽可能地增加输出阻抗。

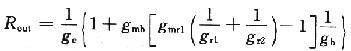

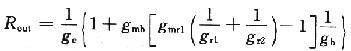

计算出输出电阻为:

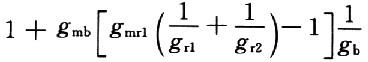

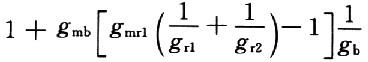

与第二代基本存储单元相比,输出电阻增大

倍。结合S2I电路与调整型共源共栅结构电路的优点,构造调整型共源共栅结构S2I存储单元。

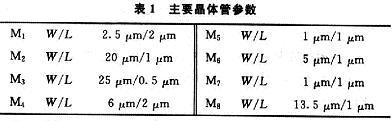

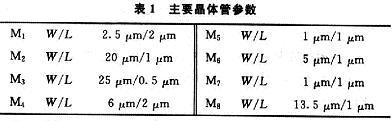

采用O.5μm CMOS工艺,level 49 CMOS模型对电路仿真,仿真参数如下:

所有NMOS衬底接地,所有PMOS衬底接电源,所有开关管宽长比均为0.5μm/O.5 μm。输入信号为振幅50μA,频率为200 kHz的正弦信号,时钟频率为5 MHz,Vref=2.4 V,VDD=5 V。表1中给出了主要晶体管仿真参数。

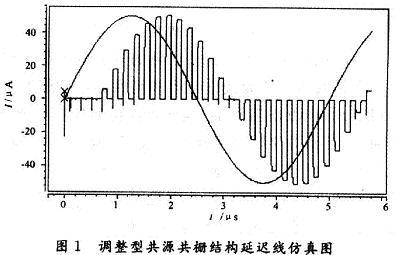

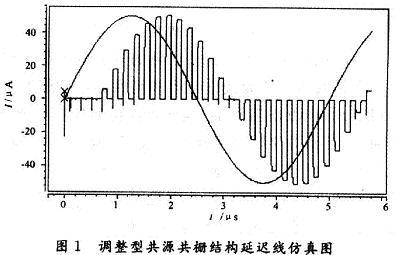

将原电路按照延迟线的结构连接并仿真,延迟3个时钟周期(相当于6个基本存储单元级联),仿真结果如图l所示。

4、结语

详细分析了第二代开关电流存储单元存在的缺点,提出了改进方法,并设计了可以延迟任意时钟周期的延迟线电路,仿真结果表明,该电路具有极高的精度,从而使该电路能应用于实际当中。其Z域传输函数为:

在实际应用中,该电路可作为离散时间系统的基本单元电路。

由于开关电流技术具有与标准数字CMOS工艺兼容的特点,整个电路均由MOS管构成,这一技术在以后的数模混合集成电路中将有广阔的发展前景。

〈烜芯微/XXW〉专业制造二极管,三极管,MOS管,桥堆等,20年,工厂直销省20%,上万家电路电器生产企业选用,专业的工程师帮您稳定好每一批产品,如果您有遇到什么需要帮助解决的,可以直接联系下方的联系号码或加QQ/微信,由我们的销售经理给您精准的报价以及产品介绍

联系号码:18923864027(同微信)

QQ:709211280