阈值电压

场效应晶体管 (FET) 的阈值电压通常缩写为 Vth 或 VGS(th),是在源极端子和漏极端子之间形成导电路径所需的最小栅源电压 (VGS)。它是保持电源效率的重要比例因子。

当提及结型场效应晶体管 (JFET) 时,阈值电压通常称为夹断电压。因为应用于绝缘栅场效应晶体管 (IGFET) 的夹断是指在高源-漏偏压下导致电流饱和行为的沟道夹断,即使电流从未关闭。与夹断不同,阈值电压一词是明确的,在任何场效应晶体管中都指代相同的概念。

晶体管阈值电压(Threshold voltage):

场效应晶体管(FET)的阈值电压就是指耗尽型FET的夹断电压与增强型FET的开启电压。

(1)对于JFET:

对于长沟道JFET,一般只有耗尽型的器件;SIT(静电感应晶体管)也可以看成为一种短沟道JFET,该器件就是增强型的器件。

(2)对于MOSFET:

*增强型MOSFET的阈值电压VT是指刚刚产生出沟道(表面强反型层)时的外加栅电压。

①对于理想的增强型MOSFET(即系统中不含有任何电荷状态,在栅电压Vgs = 0时,半导体表面的能带为平带状态),阈值电压可给出为VT = ( SiO2层上的电压Vi ) + 2ψb = -[2εεo q Na ( 2ψb )] / Ci + 2ψb ,式中Vi ≈ (耗尽层电荷Qb) / Ci,Qb =-( 2εεo q Na [ 2ψb ] ),Ci是单位面积的SiO2电容,ψb是半导体的Fermi势(等于本征Fermi能级Ei与Ef之差)。

②对于实际的增强型MOSFET,由于金属-半导体功函数差φms 和Si-SiO2系统中电荷的影响, 在Vgs = 0时半导体表面能带即已经发生了弯曲,从而需要另外再加上一定的电压——“平带电压”才能使表面附近的能带与体内拉平。

因为金属-半导体的功函数差可以用Fermi势来表示:φms = (栅金属的Fermi势ψG )-(半导体的Fermi势ψB ) ,ψb = ( kT/q ) ln(Na/ni) ,对多晶硅栅电极(通常是高掺杂),ψg≈±0.56 V [+用于p型, -用于n型栅]。而且SiO2/Si 系统内部和界面的电荷的影响可用有效界面电荷Qf表示。从而可给出平带电压为 Vfb = φms-Qf /Ci 。

所以,实际MOSFET的阈值电压为VT = -[2εεo q Na ( 2ψb )] /Ci + 2ψb +φms-Qf /Ci 。

进一步,若当半导体衬底还加有反向偏压Vbs时,则将使沟道下面的耗尽层宽度有一定的增厚, 从而使阈值电压变化为:VT = -[2εεo q Na ( 2ψb+Vbs )] /Ci + 2ψb +φms-Qf /Ci 。

在制造MOSFET时,为了获得所需要的VT值和使VT值稳定,就需要采取若干有效的技术措施;这里主要是控制Si-SiO2系统中电荷Qf :其中的固定正电荷(直接影响到VT值的大小) 与半导体表面状态和氧化速度等有关(可达到<1012/cm2); 而可动电荷 (影响到VT值的稳定性) 与Na+等的沾污有关。因此特别需要注意在氧化等高温工艺过程中的清洁度。

*耗尽型MOSFET的阈值电压VT是指刚好夹断沟道时的栅极电压。情况与增强型器件的类似。

(3)对于BJT,阈值电压VTB是指输出电流Ic等于某一定值Ict (如1mA) 时的Vbe值。由VTB = (kT/q) ln(Ict/Isn) 得知:a)凡是能导致Ic发生明显变化的因素 (如掺杂浓度和结面积等),却对VTB影响不大,则BJT的VTB可控性较好;b) VTB 对于温度很敏感,将随着温度的升高而灵敏地降低,则可用VTB值来感测温度。

阈值电压有哪些影响因素?

第一个影响阈值电压的因素是作为介质的二氧化硅(栅氧化层)中的电荷Qss以及电荷的性质。这种电荷通常是由多种原因产生的,其中的一部分带正电,一部分带负电,其净电荷的极性显然会对衬底表面产生电荷感应,从而影响反型层的形成,或者是使器件耗尽,或者是阻碍反型层的形成。Qss通常为可动正电荷。

第二个影响阈值电压的因素是衬底的掺杂浓度。要在衬底的上表面产生反型层,必须施加能够将表面耗尽并且形成衬底少数载流子的积累的栅源电压,这个电压的大小与衬底的掺杂浓度有直接的关系。衬底掺杂浓度(QB)越低,多数载流子的浓度也越低,使衬底表面耗尽和反型所需要的电压VGS越小。

所以,衬底掺杂浓度是一个重要的参数,衬底掺杂浓度越低,器件的阈值电压数值将越小,反之则阈值电压值越高。对于一个成熟稳定的工艺和器件基本结构,器件阈值电压的调整,主要通过改变衬底掺杂浓度或衬底表面掺杂浓度进行。衬底表面掺杂浓度的调整是通过离子注入杂质离子进行。

第三个影响阈值电压的因素是由栅氧化层厚度tOX决定的单位面积栅电容的大小。单位面积栅电容越大,电荷数量变化对VGS的变化越敏感,器件的阈值电压则越小。实际的效应是,栅氧化层的厚度越薄,单位面积栅电容越大,相应的阈值电压数值越低。但因为栅氧化层越薄,氧化层中的场强越大,因此,栅氧化层的厚度受到氧化层击穿电压的限制。

选用其他介质材料做栅介质是当前工艺中的一个方向。例如选用氮氧化硅 SiNxOy 替代二氧化硅是一个微电子技术的发展方向。正在研究其它具有高介电常数的材料,称为高k栅绝缘介质。

第四个对器件阈值电压具有重要影响的参数是栅材料与硅衬底的功函数差ΦMS的数值,这和栅材料性质以及衬底的掺杂类型有关,在一定的衬底掺杂条件下,栅极材料类型和栅极掺杂条件都将改变阈值电压。对于以多晶硅为栅极的器件,器件的阈值电压因多晶硅的掺杂类型以及掺杂浓度而发生变化。

可见,在正常条件下,很容易得到增强型PMOS管。为了制得增强型NMOS管,则需注意减少Qss、Qox,增加QB。采用硅栅工艺对制做增强型NMOS管和绝对值小的增强型PMOS管有利。

温度对阈值电压的影响

温度对晶体管阈值电压的影响是一种重要的影响因素,其影响的原因是由于温度的变化会导致材料本身的物理特性发生变化。

在晶体管的工作中,阈值电压是指控制电压与栅极电压之差,达到这个电压值后晶体管就开始导通。随着温度的变化,导体的电阻会发生变化,从而影响到栅极电压的大小,同时材料的电子特性也会发生变化,从而影响到阈值电压的大小。

一般来说,当温度升高时,阈值电压会降低,这意味着控制电压与栅极电压之差变小,晶体管容易被激发进入导通状态,从而会增加功耗和热量。因此,在设计中需要考虑温度对阈值电压的影响,并对芯片进行充分的温度测试和特性化,以保证芯片在不同温度下的正常工作。

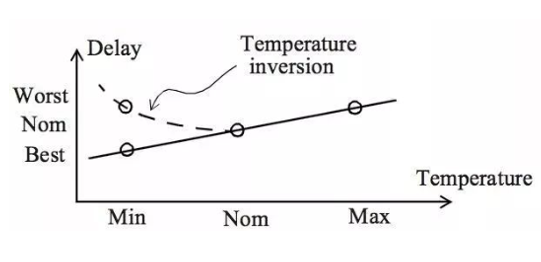

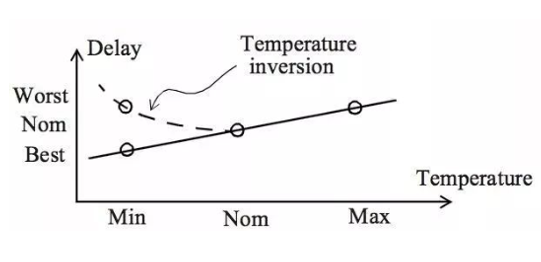

IC芯片必须适应温度不恒定的环境,当芯片运行时,由于开关功耗、短路功耗和漏电功耗会使芯片内部的温度发生变化。温度波动对性能的影响通常被认为是线性的,通常对于一个管子,当温度升高,空穴/电子的迁移率会变慢(晶格振动散射对载流子的影响越来越强),使延时增加。

注意温度翻转效应:

但在深亚微米,温度对性能的影响会导致一种温度反转现象,因为温度的升高也会使管子的阈值电压降低,较低的阈值电压意味着更高的电流,因此管子的延时减小,而在温度较低时,阈值电压带来的变化对性能的影响更大,因此器件会出现一段性能随温度下降的曲线,之后再随温度上升,至于温度翻转点跟具体的工艺相关。

这里可以理解为深亚微米工艺在较低温度时,阈值电压降低带来的daley变化占主导。

〈烜芯微/XXW〉专业制造二极管,三极管,MOS管,桥堆等,20年,工厂直销省20%,上万家电路电器生产企业选用,专业的工程师帮您稳定好每一批产品,如果您有遇到什么需要帮助解决的,可以直接联系下方的联系号码或加QQ/微信,由我们的销售经理给您精准的报价以及产品介绍

联系号码:18923864027(同微信)

QQ:709211280