CMOS工艺是在PMOS和NMOS工艺基础上发展起来的。CMOS中的C表示“互补”,即将NMOS器件和PMOS器件同时制作在同一硅衬底上,制作CMOS集成电路。CMOS集成电路具有功耗低、速度快、抗干扰能力强、集成度高等众多优点。

CMOS电路中既包含NMOS晶体管也包含PMOS晶体管,NMOS晶体管是做在P型硅衬底上的,而PMOS晶体管是做在N型硅衬底上的,要将两种晶体管都做在同一个硅衬底上,就需要在硅衬底上制作一块反型区域,该区域被称为“阱”。根据阱的不同,CMOS工艺分为P阱CMOS工艺、N阱CMOS工艺以及双阱CMOS工艺。其中N阱CMOS工艺由于工艺简单、电路性能较P阱CMOS工艺更优,从而获得广泛的应用。

cmos工艺流程

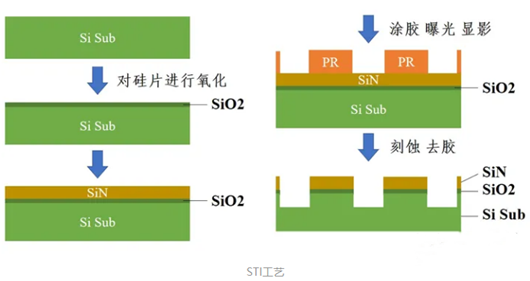

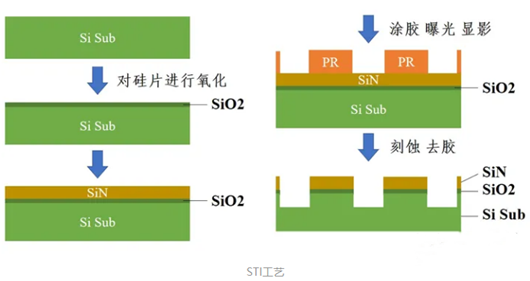

a、隔离氧化层(清洗硅片,对硅片表面进行氧化形成垫氧化层)

注:几nm厚度,作为隔离层保护有源区在去掉氮化物过程中免受化学污染,同时起到缓和硅衬底与SiN层之间应力的作用。

b、沉积SiN(数百nm厚度,采用LPCVD,即低压化学气相沉积法沉积,使用NH3与SiCl2反应,生成SiN)

注:SiN是一种坚固的掩膜材料,用于进行STI工艺时保护有源区,同时其可充当CMP的抛光阻挡材料。

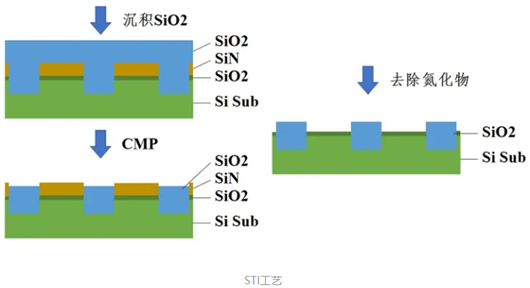

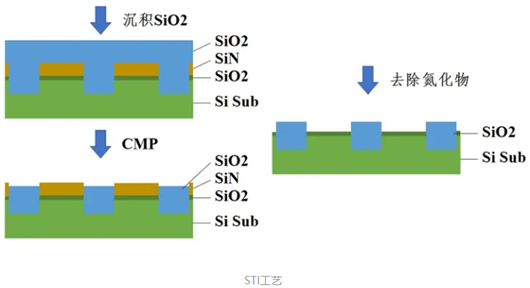

c、涂胶,曝光,显影,刻蚀掉没有光刻胶保护的区域,从而在STI区域形成浅沟槽

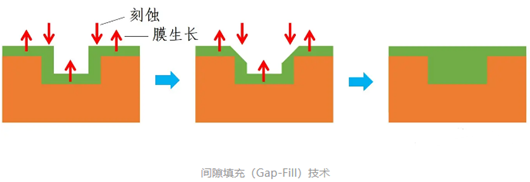

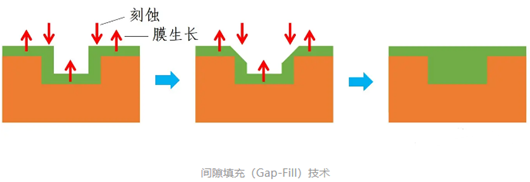

d、用CVD法沉积SiO2膜(SiO2用来阻止氧分子往有源区扩散)

使用间隙填充(Gap-Fill)技术来沉积STI的氧化层,需同时进行成膜与刻蚀工艺。

在膜生长同时进行溅射刻蚀→转角处的刻蚀速率比平坦部分高,转角处被刻蚀掉→可以避免在间隙入口处产生夹断,导致间隙填充中的孔洞→完成薄膜沉积

e、使用CMP对SiO2进行抛光(坚固的SiN充当抛光阻挡层,阻止隔离结构的过度抛光)

f、去除氮化物(热磷酸槽去除氮化物)

阱(Well)

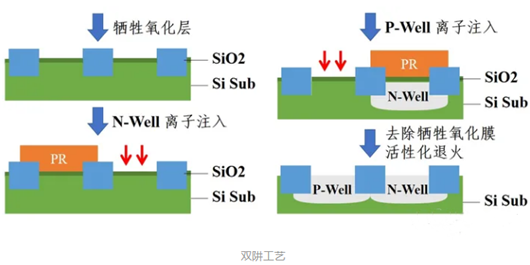

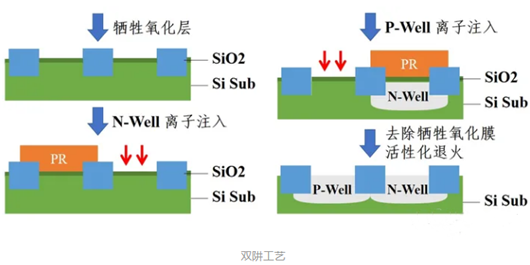

① 双阱

n型杂质的深扩散区(多数载流子为电子);p型杂质的深扩散区(多数载流子为空穴)

② 工艺流程

a、在硅晶圆上用热氧化工艺形成牺牲氧化层(作用是在离子注入形成阱时调整离子注入深度)

b、在P/N阱区域上方涂光刻胶并用光刻工艺进行曝光,显影,并用离子注入工艺注入n/p杂质,灰化去除不需要的光刻胶

c、除去牺牲氧化膜,将n型和p型阱区退火激活,形成双阱

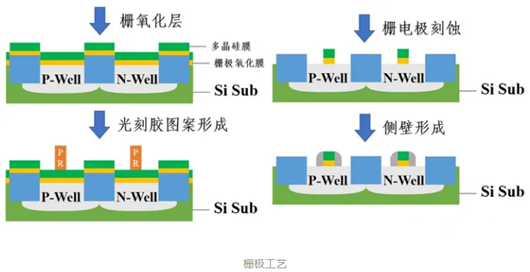

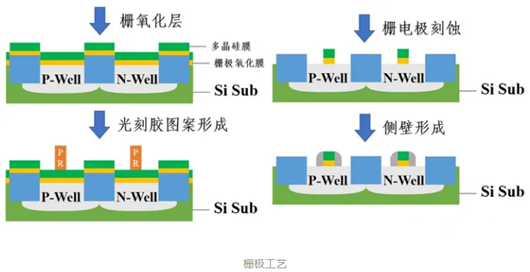

栅极

① 栅极:先进的数字电路需要高速和低压工作,需实现栅极长度的小型化(通过微细化工艺减小栅极长度)

② 自对准工艺:栅极形成是在源漏极形成之前完成,利用自对准工艺形成源漏极,可省略一道光刻工序,从而降低成本

③ 工艺流程

a、在双阱上形成栅氧化层,作为栅极材料的多晶硅层、金属硅化物的多层膜(减压CVD法)

b、用光刻工艺对栅电极进行阻挡涂改

c、对多晶硅膜进行干法刻蚀,用去胶工艺去除不需要的光刻胶

d、用等离子CVD法形成SiO2层,自对准的在栅电极两侧形成LDD膜

[缓和晶体管中微细尺寸的栅电极附近的电场]

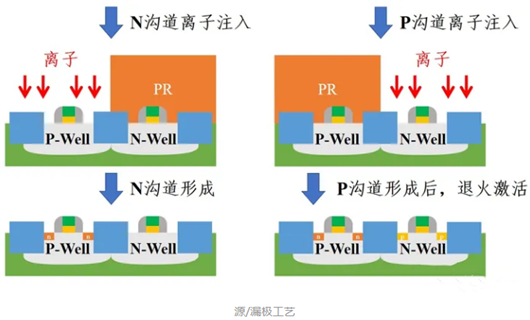

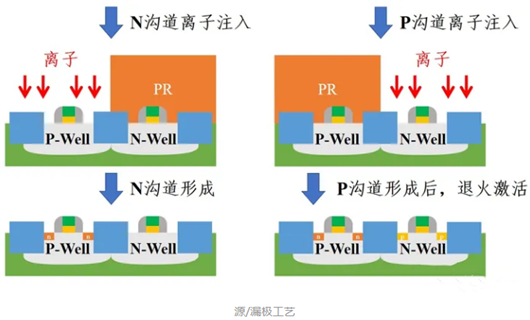

源极/漏极

① 源极与漏极

MOS管通过施加到栅极的电压执行开关操作,以打开和关闭源极与漏极之间的电流。

② 工艺流程

a、通过光刻工艺在n阱区域上覆盖光刻胶,并将n型杂质离子注入p型区域

b、使用高电流型的离子注入设备向源漏极注入高浓度的杂质

c、灰化去除不需的光刻胶

d、n阱区域同理

e、退火激活形成n型和p型晶体管的源漏极区域

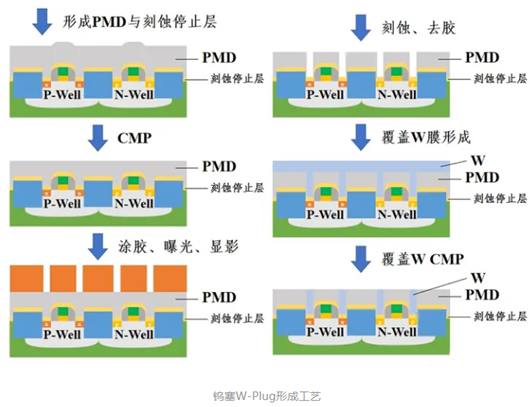

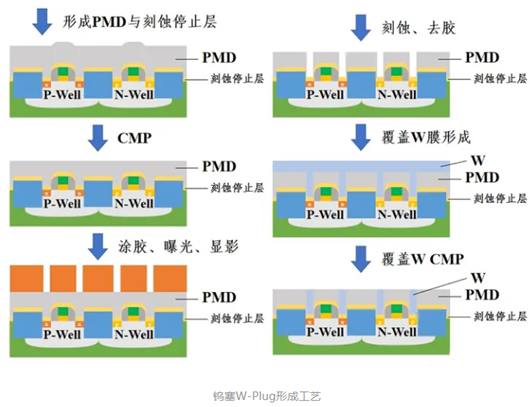

电极形成(钨塞W-Plug形成)

工艺流程

a、用等离子CVD法形成刻蚀停止层和隔离层(隔离层是金属布线层形成之前的绝缘层,称为PMD[Pre Metal Dielectrics])

b、用CMP工艺使得隔离层平坦化(受栅电极的影响,上部的形状会产生凸起)

c、用光刻法形成接触孔的图形(微细尺寸的源漏极和接触必须连接上,且要采取最小的布线间距)

d、用光刻胶作为掩膜来刻蚀隔离层,穿透形成接触孔

e、灰化去除不需要的光刻胶

f、在接触孔内形成TiN/Ti等黏附层和覆盖W层

注:黏附层将隔离层和W膜更好地黏接到一起,用溅射工艺生成;覆盖式W膜用CVD法形成

g、用CMP工艺去除PMD上多余的W层和黏附层,实现W塞

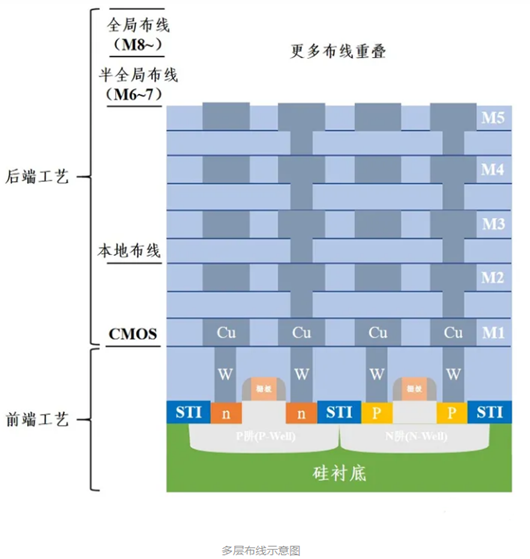

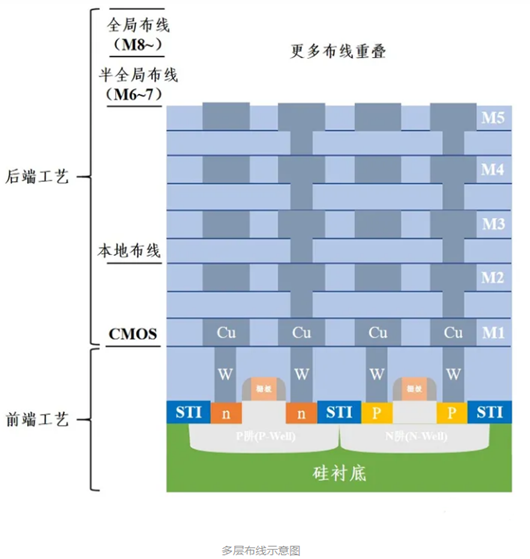

后端工艺

1、Why使用多层布线

在先进的逻辑IC中,把已经验证完成的IP进行整合,进而完成数字IC的设计。新的电路的验证需要花费大量的时间,通常是把各种各样的电路模块通过布线连接到一起来实现该LSI。

2、多层布线示意图

〈烜芯微/XXW〉专业制造二极管,三极管,MOS管,桥堆等,20年,工厂直销省20%,上万家电路电器生产企业选用,专业的工程师帮您稳定好每一批产品,如果您有遇到什么需要帮助解决的,可以直接联系下方的联系号码或加QQ/微信,由我们的销售经理给您精准的报价以及产品介绍

〈烜芯微/XXW〉专业制造二极管,三极管,MOS管,桥堆等,20年,工厂直销省20%,上万家电路电器生产企业选用,专业的工程师帮您稳定好每一批产品,如果您有遇到什么需要帮助解决的,可以直接联系下方的联系号码或加QQ/微信,由我们的销售经理给您精准的报价以及产品介绍

联系号码:18923864027(同微信)

QQ:709211280