TTL电平

TTL电平信号在电路设计中被利用的最多是因为通常数据表示采用二进制规定,+5V等价于逻辑"1",0V等价于逻辑"0",这被称做TTL(晶体管-晶体管逻辑电平)信号系统,这是计算机处理器控制的设备内部各部分之间通信的标准技术。

TTL集成电路的全名是晶体管-晶体管逻辑集成电路(Transistor-Transistor Logic),主要有54/74系列标准TTL、高速型TTL(H-TTL)、低功耗型TTL(L-TTL)、肖特基型TTL(S-TTL)、低功耗肖特基型TTL(LS-TTL)五个系列。

标准TTL:输入高电平最小2V,输出高电平最小2.4V,典型值3.4V,输入低电平最大0.8V,输出低电平最大0.4V,典型值0.2V。

肖特基型TTL(S-TTL):输入高电平最小2V,输出高电平最小Ⅰ类2.5V,Ⅱ、Ⅲ类2.7V,典型值3.4V,输入低电平最大0.8V,输出低电平最大0.5V。

低功耗肖特基型TTL(LS-TTL):输入高电平最小2V,输出高电平最小Ⅰ类2.5V,Ⅱ、Ⅲ类2.7V,典型值3.4V,输入低电平最大Ⅰ类0.7V,Ⅱ、Ⅲ类0.8V,输出低电平最大Ⅰ类0.4V,Ⅱ、Ⅲ类0.5V,典型值0.25V。

TTL优点:速度快

TTL缺点:无法大规模集成,因为三极管的静态电流损耗很大,且TTL输入只是双极晶体管的基极,需要一些电流来打开它。输入电流的大小取决于内部电路,最高可达1.6mA。当许多TTL输入连接到一个TTL输出时,这就成了一个问题,这通常只是一个上拉电阻或一个相当差的驱动高侧晶体管。

CMOS电平

COMS集成电路是互补对称金属氧化物半导体(Compiementary symmetry metal oxide semicoductor)集成电路的英文缩写,电路的许多基本逻辑单元都是用增强型PMOS晶体管和增强型NMOS管按照互补对称形式连接的,静态功耗很小。

COMS电路的供电电压VDD范围比较广在+5--+15V均能正常工作,电压波动允许±10,当输出电压高于VDD-0.5V时为逻辑1,输出电压低于VSS+0.5V(VSS为数字地)为逻辑0。

CMOS优点:静态电流几乎为0,损耗小,静态功耗接近为0,可在芯片里大规模集成。CMOS晶体管是场效应的,换句话说,栅极处存在的电场足以影响半导体通道进入导通。理论上,除了栅极的小漏电流外,不产生电流,漏电流通常在皮安培或纳安培量级。

CMOS缺点:由于CMOS芯片有一定的输入电容,因此上身时间有限,速度相对TTL较慢为了确保在高频下上升时间快,CMOS需要一个大电流,在MHz或GHz频率下可以达到几安培的数量级。这个电流只有在输入必须改变状态时才被消耗,不像TTL,偏置电流必须与信号一起存在。

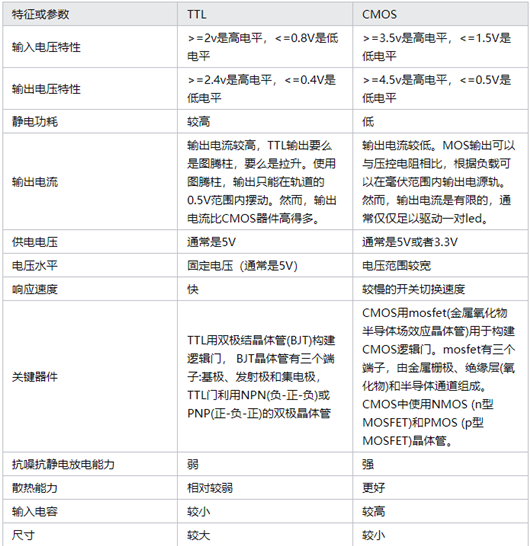

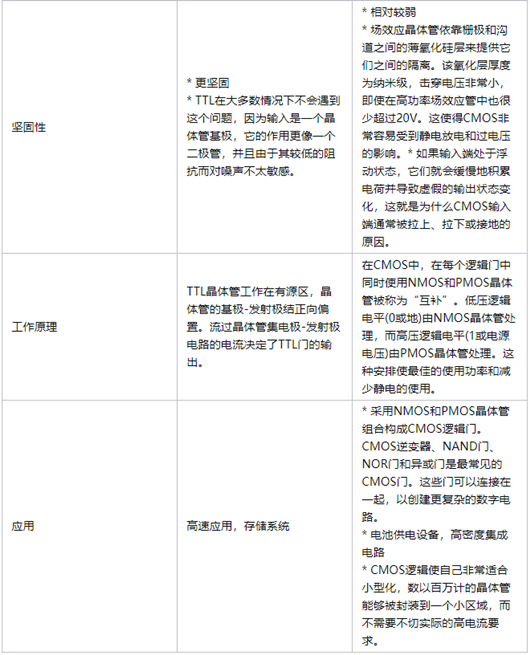

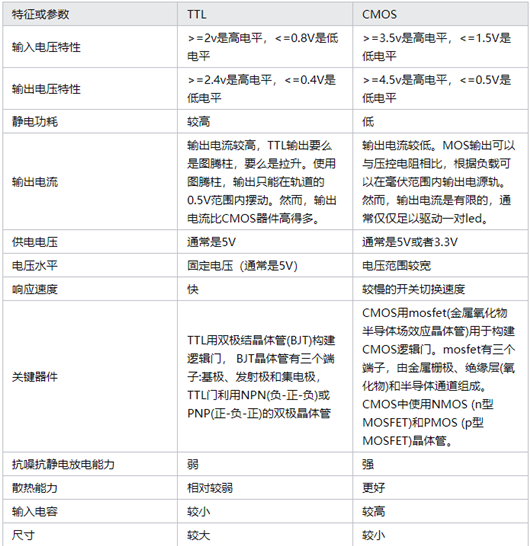

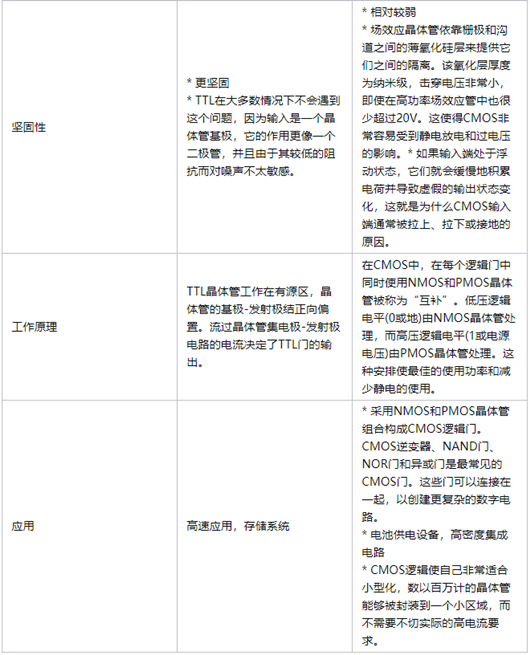

ttl与cmos的区别对比

1、CMOS是场效应管构成,TTL为双极晶体管构成。

2、COMS的逻辑电平范围比较大,一般在5V~15V,TTL只能在5V下工作。

3、CMOS的高低电平之间相差比较大、抗干扰性强,TTL则相差小,抗干扰能力差 。

4、CMOS功耗很小,TTL功耗较大,一般在1~5mA/门。

5、CMOS的工作频率较TTL略低,但是高速CMOS速度与TTL差不多相当。

6、TTL电路是电流控制器件,而coms电路是电压控制器件。

7、TTL电路的速度快,传输延迟时间短(5-10ns),但是功耗大。COMS电路的速度慢,传输延迟时间长(25-50ns),但功耗低。COMS电路本身的功耗与输入信号的脉冲频率有关,频率越高,芯片集越热,这是正常现象。

CMOS和TTL的共同之处

CMOS和TTL都不能让输入端口悬空。

因为端口悬空会导致意想不到的后果,比如受到噪声干扰,增加功耗。

对于CMOS的输入端,应该按照逻辑需求将他们要么和VCC连接,要么和GND连接。

对于TTL的输入端,应该将他们和VCC连接,或者通过一个下拉电阻实现低电平。不能直接将TTL输入端和GND直接连接,因为这样会导致过电流,损坏器件。

〈烜芯微/XXW〉专业制造二极管,三极管,MOS管,桥堆等,20年,工厂直销省20%,上万家电路电器生产企业选用,专业的工程师帮您稳定好每一批产品,如果您有遇到什么需要帮助解决的,可以直接联系下方的联系号码或加QQ/微信,由我们的销售经理给您精准的报价以及产品介绍

联系号码:18923864027(同微信)

QQ:709211280