体效应详解

在许多应用中,源极直接连接到底物(体极)B极,使得底物和沟道之间的pn结是零电压偏置。此时底物在电路中不发挥任何作用,可以被忽略。

在集成电路中,底物通常被大量的MOS所共用。为了保证底物和所有沟道之间的pn结都是截止状态,底物在NMOS中通常被连接到最小负电压源(在PMOS中连接到最大正电压源)。在这种情况下,反向偏置的pn结会对元器件造成影响。为了说明这一点,考虑一个NMOS并且让它的底物电压比源极电压低(此时pn结反向偏置)。反向偏置的电压将会扩大耗散区的体积,这回加深沟道的深度,这会导致iD增大,为了使得MOS回到原来的状态上,就必须增大 vGS 。

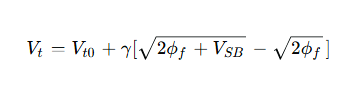

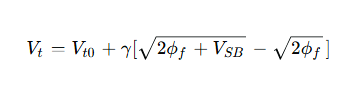

电压VSB可以看做是改变了阈值电压Vt,关系由下面的表达式给出:

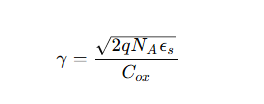

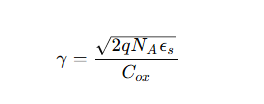

在这里Vt0是在VSB= 0条件下的阈值电压,?f是一个物理参数一般情况是0.6V,γ是制作工艺参数,由下面的表达式给出:

在这里 q是电子电荷量,NA是p类型底物的掺杂浓度,?s是硅的介电常数。

上式反应了增大VSB会导致 Vt的增加,尽管VGS保持恒定的情况下也会增大ID 。换句话说,VBS同样能控制ID的大小,因此体极和栅极具有相同的控制ID的能力,这个效应称为体效应 。这里 γ 称为体效应参数。

MOS管体效应衬偏效应

当MOS管源端电势大于衬底电势(VS>VB )时,栅下面的表面层中将有更多的空穴被吸收到衬底上,留下更多不能移动的负离子(负电中心),使得耗尽层展宽。阈值电压升高。

1.为什么需要源端电势大于衬底电势?

因为对于CMOS芯片来说,特别是数字芯片来说,其衬底电压会存在一定的波动,如果不对衬底电压进行限制,则可能出现衬底电压大于源端电压的情况,使得PN结正偏。MOS管失效,所以需要在衬底与源之间加上适当的反偏电压,以保证MOS的工作状态。这个电压也时常被称为衬偏电压。

2.体效应有什么影响?

1、耗尽层展宽使得阈值电压VT升高,进而影响器件的GM和IDS等性能。因为这些器件性能均与VT相关。

2、衬底掺杂浓度越高,衬偏效应就越明显,以典型的CMOS工艺为例,PMOS的衬偏效应会大于普通NMOS的衬偏效应,因为制作PMOS的n阱掺杂大于衬底掺杂(掺杂浓度越高,耗尽层越窄,耗尽层电容越大,使得n阱与衬底隔离),能够单独控制电压。

3、当芯片工作时,MOS管源极的电压会不断的变化,使得源衬之间的电压也在不断变化。这就是背栅调制效应,即出现了JFET的功能。

4、背栅调制作用使得沟道中的面电荷密度也随着源端电压的变化不断变化,出现了电容效应。称为衬偏电容,该电容会明显影响器件的开关速度。

5、背栅调制效应作用对应会产生一个交流电阻。该电阻会使的MOS管的输出电阻降低,电压增益下降。

在设计中如何降低体效应的影响?

1、将源端与漏端短接。这也是采用的方法,如将NMOS的源漏都接地,将PMOS的源漏都接VDD。

2、改进电路结构。对于某些不能将源漏短接的情况,便只能在电路结构层面上进行改进。如在CMOS中采用有源负载。

〈烜芯微/XXW〉专业制造二极管,三极管,MOS管,桥堆等,20年,工厂直销省20%,上万家电路电器生产企业选用,专业的工程师帮您稳定好每一批产品,如果您有遇到什么需要帮助解决的,可以直接联系下方的联系号码或加QQ/微信,由我们的销售经理给您精准的报价以及产品介绍

联系号码:18923864027(同微信)

QQ:709211280