MOS管的GIDL效应是指在栅极电压较高的情况下,绝缘层下的沟道区域会发生漏电现象的现象。这种现象是由于高电场导致绝缘层中的电子发生穿隧效应,从而形成漏电流。

GIDL效应会导致器件的功耗增加、性能下降,并可能引起电流漂移现象。针对GIDL效应的影响和问题,研究人员提出了一些解决方案,包括使用高介电常数的材料来减小电场强度、优化沟道结构和引入电场屏蔽层等方法。此外,还有其他一些方法可以应对GIDL效应,例如采用低功耗工艺、优化栅极结构和控制栅极电压等。

GIDL(gate-induced drain leakage) 是指栅诱导漏极泄漏电流,对MOSFET的可靠性影响较大。

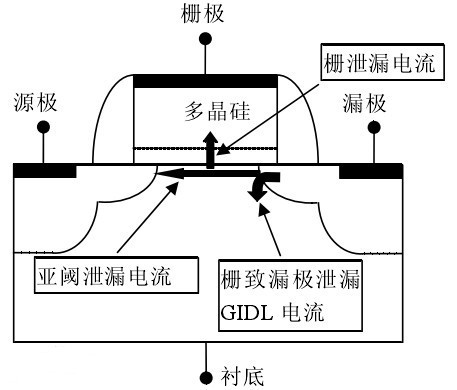

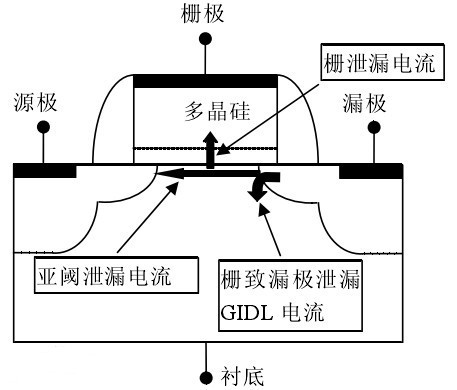

MOSFET 中引发静态功耗的泄漏电流主要有:源到漏的亚阈泄漏电流,栅泄漏电流,发生在栅漏交叠区的栅致漏极泄漏 GIDL 电流,如图所示。在这些泄漏电流中,在电路中器件处于关态或者处于等待状态时,GIDL 电流在泄漏电流中占主导地位。

GIDL 隧穿电流

当栅漏交叠区处栅漏电压 VDG很大时,交叠区界面附近硅中电子在价带和导带之间发生带带隧穿形成电流,我们把这种电流称之为 GIDL 隧穿电流。随着栅氧化层越来越薄,GIDL 隧穿电流急剧增加。

GIDL 产生电流

漏 pn 结由于反偏,产生率大于复合率,在栅控制下,硅和二氧化硅界面处陷阱充当产生中心而引发的一种栅诱导的漏极泄漏电流。

栅致漏极泄露电流,gate induced drain leakage (GIDL,/GIDL)

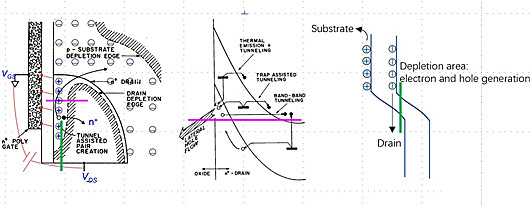

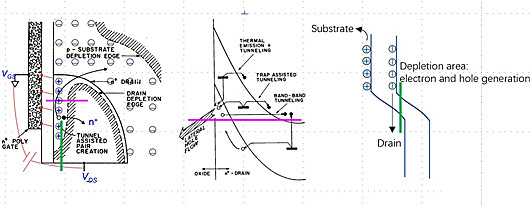

栅致漏极泄露电流是由MOS晶体管漏极结中的高场效应引起的。由于G与D重叠区域之间存在大电场而发生隧穿并产生电子-空穴对,其中包含雪崩隧穿和BTBT隧穿。由于电子被扫入阱中,空穴积累在漏中形成/GIDL。

以NMOS为例,当gate不加压或加负压,drain端加高电压, 使得gate和drain的交叠区域出现了一个从drain指向gate的强电场,靠近gate oxide 附近出现强耗尽区,形成电势变化非常陡的类p+-n+结—横向和纵向的图;(一定是gate与drain要有重叠吗?要有交叠,这也是GIDL管的来源),引起了耗尽区电子空穴分离,载流子跃迁,电子流向drain端,空穴被扫入基底,由此形成漏电流。

NMOS 中 GIDL 图解 (横向、纵向)

前提条件:

1) 亚阈值区

2)Drain和gate有交叠,GIDL产生处有pn结

3)强漏电场

Impact in MOS:亚域区漏电流,增大静态功耗

Mitigation in MOS: LDD, 交叠区轻掺杂,使电势缓变,跃迁几率减小,漏电流减小

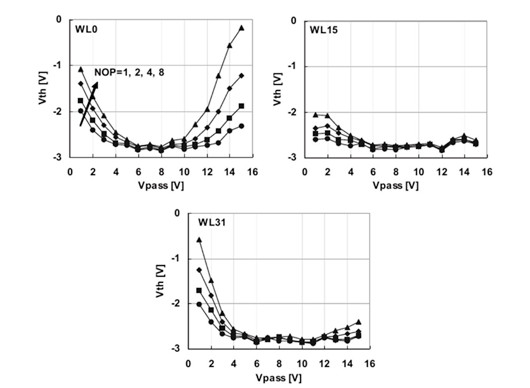

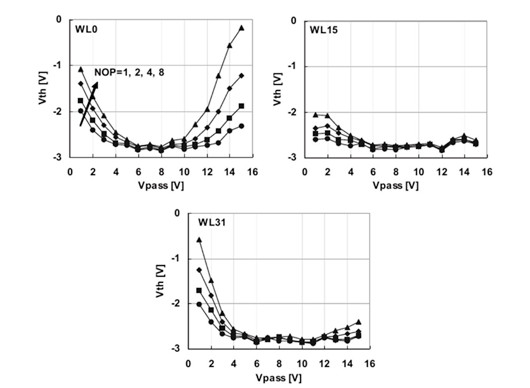

Impact in NAND:在program时,被inhibit string 发生HCI效应, 边缘WL Vt上浮 (不被inhibit的string, 不存在静电压差,这种效应应该较弱)

Mitigation in MOS: 设置边缘dummy WL

Application in NAND:GIDL erase,3D NAND中, Pwell erase 需结合SEG工艺,工艺复杂,因此越来越多的制造商开始使用GIDL erase,即利用GIDL效应产生电子空穴对,将空穴扫入channel中,实现块擦除。

〈烜芯微/XXW〉专业制造二极管,三极管,MOS管,桥堆等,20年,工厂直销省20%,上万家电路电器生产企业选用,专业的工程师帮您稳定好每一批产品,如果您有遇到什么需要帮助解决的,可以直接联系下方的联系号码或加QQ/微信,由我们的销售经理给您精准的报价以及产品介绍

联系号码:18923864027(同微信)

QQ:709211280