功耗

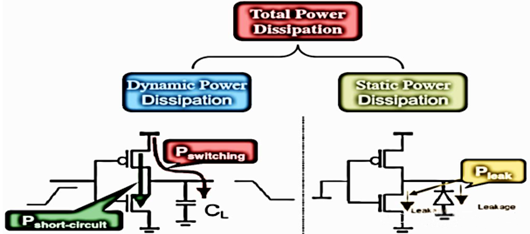

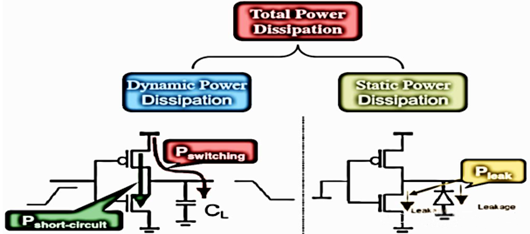

功耗 = 静态功耗 + 动态功耗

= 静态功耗 + 转换功耗 + 短路功耗

功耗源

功耗的本质是能量耗散。由能量守恒定律可知,能量只能从一种形式转成另一种形式,能量的总量不变。芯片耗散的电能主要转化成热能。如果一颗芯片的功耗过大,容易导致工作时温度过高,造成功能失效,甚至晶体管失效。因此,减小芯片功耗是很重要的一个任务。静态功耗以及动态功耗是两个主要的功耗源。

动态功耗

P_dynamic=k*C*V*V*f+m*V*I_sc,和电压、负载电容、工作时钟频率、信号翻转率、短路电流有关;

电压角度:

(1)降低工作电压;

(2)多电压域;

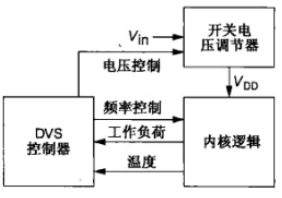

(3)动态电压缩放DVS技术(处理器在不同工作模式下使用不同电压);

(4)电源关断技术,power-gating;

负载电容角度:与工艺有关

(1)按比例缩小集成度,降低器件电容;

(2)多芯片系统中,可以考虑多芯片封装,减低接口间电容;

(3)合理的布局布线;

工作时钟频率角度:

(1)降低工作频率;

(2)多时钟域;

(3)门控时钟,clockgating;

数据翻转率角度:

(1)使用格雷码等状态翻转比较少的编码;

(2)数据不操作说,保持上次的值,而不是强制置0或者置1;

(3)使用使能信号、片选信号,减少不必要的切换;

1.动态功耗

动态功耗来源于:

(1)当门翻转时,负载电容充电和放电,称为翻转功耗

(2)pmos和nmos管的串并联结构都导通时的有短路电流,称为短路功耗。

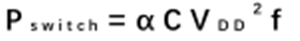

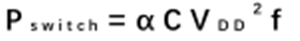

1.1翻转功耗翻转功耗可以用如下公式表示:

α称为活动因子,是电路节点从0跳变至1的概率。时钟的活动因子为1,因为它在每个周期都有上升和下降。大多数数据的活动因子为0.5,每周期只跳变一次。

C称为负载电容。

有以下办法可以降低翻转功耗:

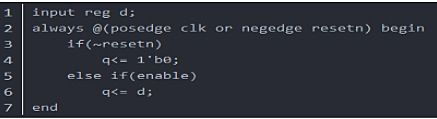

(1)使用门控时钟降低活动因子是降低功耗的非常有效的办法,如果一个电路的时钟完全关断,那么它的活动因子和动态功耗将降为0。Verilog在设计寄存器时采用下面写法可以综合成一个带门控的寄存器。

(2)减小毛刺毛刺会增大活动因子,有可能使门的活动因子增加到1以上。

(3)减小负载电容电容来自于电路中的连线以及晶体管。缩短连线长度,良好的平面规划和布局可以使连线电容减小。选择较小的逻辑级数以及较小的晶体管可以减小器件的翻转电容。

(4)电压域动态功耗与电压有平方的关系,降低电源电压可以显著降低功耗。将芯片划分成多个电压域,每个电压域可以根据特定电路的需要进行优化。例如,对于存储器采用高电源电压来保证存储单元的稳定性,对于处理器采用中等大小的电压,对运行速度较低的IO外围电路采用低电压。解决跨电压域信号传输的方法是使用电平转换器。

(5)动态电压调整DVSCPU处理不同的任务有不同的性能要求。对于低性能要求的任务,可以使时钟频率降低到足以按预定时间完成任务的最低值,然后使电压降低到该频率下工作所需要的最小值就可以节省大量的能耗。

(6)降低频率动态功耗正比于频率,芯片只应当工作在所要求的频率下,不能比所要求的还要快。由前面小结可以,降低频率还可以采用较低的电源电压,大大降低功耗。

(7)谐振电路谐振电路通过使能量在储能元件如电容或电感之间来回传送而不是将能量泄放到来减小翻转功耗。

1.2短路功耗

短路功耗发生在当输入发生翻转时,上拉和下拉网络同时部分导通的时候。如果输入信号翻转速率比较慢,那这两个网络将同时导通较长的一段时间,短路功耗也会比较大,增大负载电容可以减小短路功耗,原因是负载较大时,输出在输入跳变期间只翻转变化很小的一个量。

短路电流一般为负载电流的10%。当输入边沿变化速度很快时,短路功耗一般只占翻转功耗的2%-10%。

〈烜芯微/XXW〉专业制造二极管,三极管,MOS管,桥堆等,20年,工厂直销省20%,上万家电路电器生产企业选用,专业的工程师帮您稳定好每一批产品,如果您有遇到什么需要帮助解决的,可以直接联系下方的联系号码或加QQ/微信,由我们的销售经理给您精准的报价以及产品介绍

〈烜芯微/XXW〉专业制造二极管,三极管,MOS管,桥堆等,20年,工厂直销省20%,上万家电路电器生产企业选用,专业的工程师帮您稳定好每一批产品,如果您有遇到什么需要帮助解决的,可以直接联系下方的联系号码或加QQ/微信,由我们的销售经理给您精准的报价以及产品介绍

联系号码:18923864027(同微信)

QQ:709211280