lvds电平

LVDS :低电压差分信号(Low-Voltage Differential Signaling)是一种信号传输模式的电平标准,LVDS传输支持速率一般在155Mbps(大约为77MHz)以上。它采用极低的电压摆幅高速差动传输数据(采用CMOS 工艺的低电压差分信号器件),实现点对点(或则点对多:M-LVDS)的连接,具有低功耗、低误码率、低串扰和低辐射等优点。

LVDS 器件的传输机制是把 TTL 逻辑电平转换成低电压差分信号,以便于高速传输。与传统的 ECL逻辑相比,它采用 CMOS 工艺,其电压摆幅更低(LVDS只有 400mV,ECL 为 800mv),动态功耗更小(输出电流 3~5mA,只有 ECL 电路的 1/7),低 EMI,价格更低,因而在中等频率(几百M~几GHz)差分信号应用上具有较大的优势。

lvds电平标准

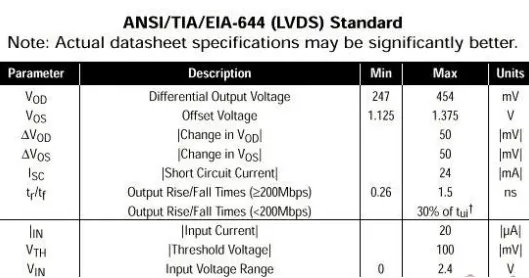

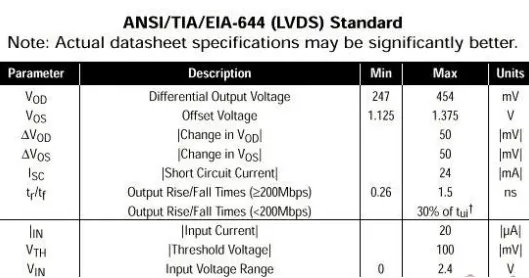

LVDS技术规范有两个标准,即TIA(电讯工业联盟)/EIA(电子工业联盟)的ANSI/TIA/EIA-644标准(LVDS也称为RS-644接口)与IEEE 1596.3标准。

标准参数的制定一方面取决于器件的制造工艺水平,另一方面取决于该标准面向的应用场景的性能要求。这意味着在不同的参数里,思考参数的取值的方法可能大相径庭。

LVDS电路结构

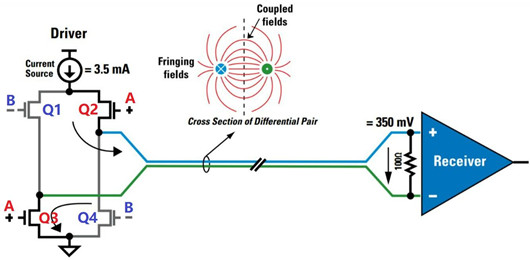

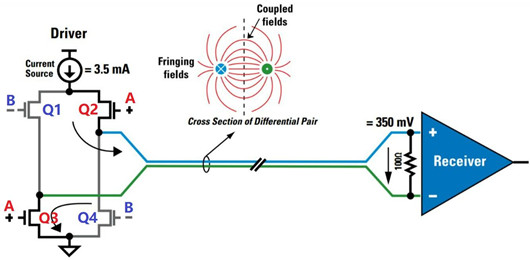

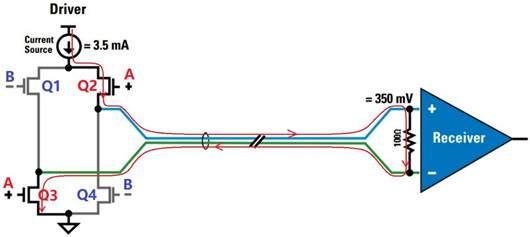

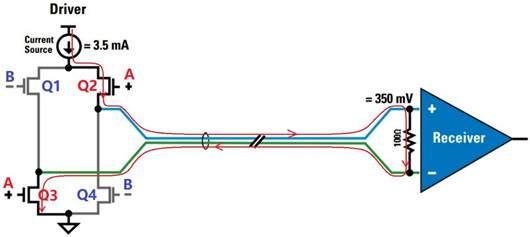

下图为典型的LVDS电路,采用一对差分信号线传输数据;通过驱动3.5mA的稳定电流源,以350mV低振幅(100Ω终端匹配)的差动信号来高速传送数据。其数据传输速度在规格内限定最大为655Mbit/秒,但这并不是极限值。通过各半导体厂商改进,可以实现3Gbit/秒左右的高速传输速度。

LVDS的输出端驱动是一个3.5mA的电流源,并由两组MOS管(4个)组成一对发送输出;

当A+导通,B-断开时:

1, 电流从右上角Q2(A+ MOS管)驱动出到蓝色传输线,即右上A+ MOS管电流方向是:电流源(Driver)右上A+ MOS管蓝色传输线100Ω终端电阻;

2, 左下角Q3(A+ MOS管)驱动接至GND,所以此时电流从绿色传输线通过左下角Q3流出到GND;左下A+ MOS管电流方向是:GND左下A+ MOS管绿色传输线100Ω终端电阻;

3, 整个电流通路最终电流在100Ω终端电阻侧导通,并形成输出电压:3.5mA *100Ω = 350mV。

因为传输线提供的100Ω阻抗是交流阻抗,对于直流来说是传输线是高阻抗,所以终端必须有100Ω端接电阻来提供信号固定电平状态下的回流,以保证输出电压;

需要再次强调的是:3.5mA电流从电源源流出到蓝色传输线,和绿色传输线3.5mA电流流入GND,这两者同时发生的,才能保证信号边沿的同步;驱动电流的路径并非是:电流源Q2蓝色传输线100Ω终端电阻绿色传输线Q3GND。

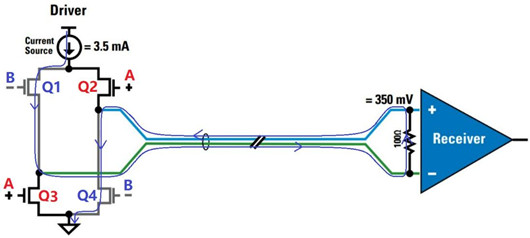

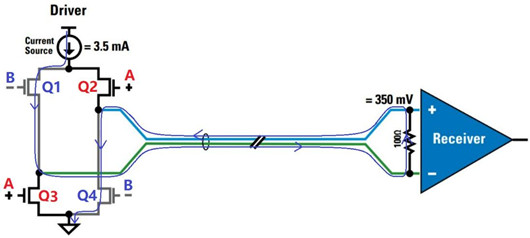

当B-导通,A+断开时:

1, 此时3.5mA驱动电流从左上角Q1(B- MOS管)流出,并流入绿色传输线;

2, 同时蓝色传输线电流流入右下角Q4(B- MOS管);

具体电流传输的方向,如上。

3, 电流通路最终电流还是在100Ω终端电阻侧导通,但是电流方向与“A+导通,B-断开”相反,并形成反向的输出电压:-3.5mA *100Ω = -350mV。

最终在输出端形成 +350mV和-350mV信号摆幅的差分输出。

〈烜芯微/XXW〉专业制造二极管,三极管,MOS管,桥堆等,20年,工厂直销省20%,上万家电路电器生产企业选用,专业的工程师帮您稳定好每一批产品,如果您有遇到什么需要帮助解决的,可以直接联系下方的联系号码或加QQ/微信,由我们的销售经理给您精准的报价以及产品介绍

联系号码:18923864027(同微信)

QQ:709211280