在电路设计中,常常会出现发送接收两方的信号电平不匹配的情况,例如在I2C bus上,处理器电平一般是1.8V,但EEPROM则一般还是3.3V。

在这种情况发生的时候,逻辑上有两种解决方法: 1. 调整某一方的电平使其匹配 2. 将两方芯片的高电平输出解耦,通过中间器件使其正常工作。

两种解决方法

调整某一方的电平使其匹配

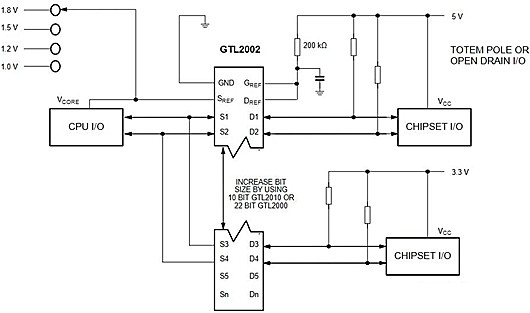

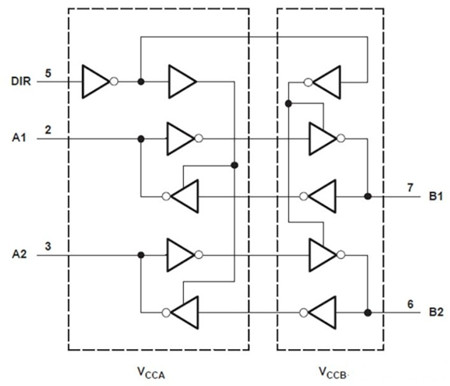

对于一般的设计或者常规思路,调整电平是最简单的,无非增加一个电平转换芯片,一种通用的电平转换芯片如下,只需要做好reference voltage与input signal voltage的匹配,其他的芯片内部的逻辑电路就可以完成了。

在这种芯片内部,一般也是几个逻辑器件,只是将某一方向的最后一个或者两个管子的Vin换成了对应的输出而已。这本质上还是第二种方法的应用。

高电平输出解耦

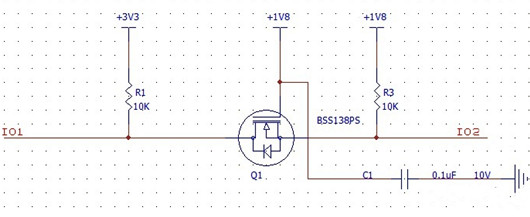

说起来高大上,输出解耦,其实就是一个三极管隔离电路,只是这个电路具体细节分析起来相对麻烦一点,并且对于使用的MOS管参数也要仔细分析。

比如下图电路。 首先查一下Q1的参数, Vgsth = 0.9V.min Vsd = 1.1V.max

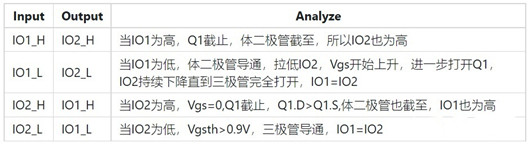

对于输入输出,有四种情况:

要点

对于Q1,Vgs在静态要等于0V,最好Gate和Source使用同源电平,Vsd在静态要小于手册里Vsd的值,否则会造成管子打开关不上的情况。静态状态下Vs<Vd。

有种设计会使用体二极管的单向导通防止漏电,这种情况下也必须满足要点1的要求;当漏电与体二极管方向发生冲突的时候,要优先满足体二极管方向。

C1是为了上电瞬间打开管子的曲线平滑一些,同时让输入输出电平稳定后再提供Gate端电平。

〈烜芯微/XXW〉专业制造二极管,三极管,MOS管,桥堆等,20年,工厂直销省20%,上万家电路电器生产企业选用,专业的工程师帮您稳定好每一批产品,如果您有遇到什么需要帮助解决的,可以直接联系下方的联系号码或加QQ/微信,由我们的销售经理给您精准的报价以及产品介绍

联系号码:18923864027(同微信)

QQ:709211280