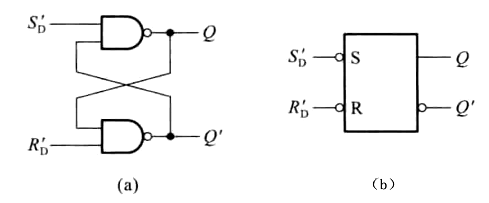

与非门R-S锁存器

R-S锁存器是静态存储单元中最基本的一种电路结构,通常由两个或非门或者与非门组成,下图为与非门搭建R-S锁存器的电路结构图。

基本RS锁存器由电平触发,并且有一个重要的约束条件:/SD和/RD不能同时为零。

即存在约束条件 RD ·SD=0

其中Q为初态,Q*为次态

电平触发器

触发器通常分为电平触发,边沿触发,脉冲触发

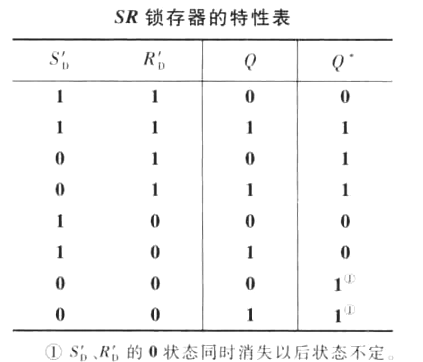

电平触发RS锁存器

由两个与非门和SR锁存器组成电平触发器

只有当CLK=1为高电平时,G3、G4输出端才收R和S输入端控制

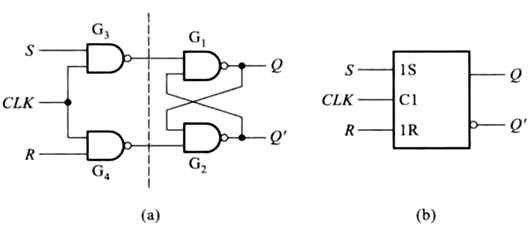

带异步复位,异步置位的电平触发RS锁存器

只需在/SD和/RD加入低电平,即可将触发器置1和置0;在正常由时钟信号控制情况下/SD和/RD应为高电平。

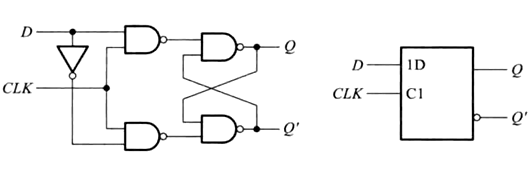

电平触发D触发器

电平触发D触发器,也称D型锁存器

若D为1,在CLK=1期间,输出端Q为1,在CLK=0低电平期间,输入端D无效,输入端与非门置1,输出端Q保持不变;若D为0,在CLK=1期间,输出端Q为0,在CLK=0低电平期间,输出端Q保持0不变,完成了锁存功能。

边沿触发器

为提高触发器可靠性,增强抗干扰能力,希望触发器的次态仅仅取决于CLK信号上升沿或下降沿时刻输入信号的状态,而之前和之后的状态不对输出造成影响。

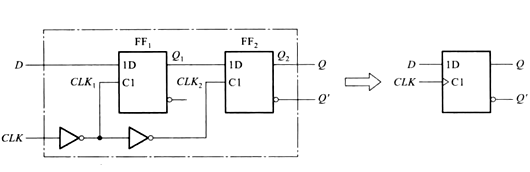

下图为由两个电平D触发器搭建的边沿触发器

当CLK为低电平时,CLK1为高电平,FF1的输出Q跟随D变化而变化,保持Q1=D,此时CLK2为低电平,FF2的输出Q2保持原来的状态不变。

当CLK由低电平变高电平时,CLK1变为低电平,Q1保持为CLK上升沿到达前瞬间输入端D的状态(这也时setup存在的原因),此后不随D的状态而改变。而此时CLK2变为高电平,Q2跟随当前时钟沿传输的的数据Q1变化,此时Q被置位成时钟上升沿瞬间D端的状态,而于之后D的状态无关。

〈烜芯微/XXW〉专业制造二极管,三极管,MOS管,桥堆等,20年,工厂直销省20%,上万家电路电器生产企业选用,专业的工程师帮您稳定好每一批产品,如果您有遇到什么需要帮助解决的,可以直接联系下方的联系号码或加QQ/微信,由我们的销售经理给您精准的报价以及产品介绍

联系号码:18923864027(同微信)

QQ:709211280