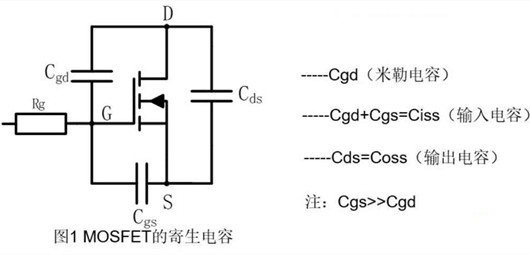

结电容”的定义适用于所有的FET,并不局限于VMOS,也适用于所有的VMOS晶体管,只是测定方法与标识方法有差异。实际上结电容还包括引线电极与管芯之间的电容、管芯各组成部分之间、管芯与封装之间的分布电容。

Cgd在BJT(双极性晶体管)中也称为米勒电容(Cbc),对FET而言也同样可以这样称呼,二者在功能上是等同的。

尽管结电容的容墩非常小,对电路稳定性的影响却是不容忽视的,处理不当往往会引起高频自激振荡。更为不利的是,栅控器件的驱动本来只需要一个控制电压而不需要控制功率,但是下作频率比较高的时候,结电容的存在会消耗可观的驱动功率,频率越高,消耗的功率越大。

在实践中,为了分析问题的方便,一般并不直接用结电容参数进行分析,而是重新定义了三个变量,统称为分布电容,具体如下。

输入电容(lnput Capacitance):Ciss=Cgd十Cgs

输出电容(Output Capacitance):Cdss=Cgd+Cds

逆导电容( Reverse Transfer Capacitance):Crss=Cgd

之所以引入分布电容的概念,是因为结电容是由晶体管的材料和结构决定的,不能全面反映对晶体管电路的实际影响。分布电容则主要反映结电容对下作电路的影响。

无论是CiSS、Coss、Crss中的哪一个,我们都希望他们尽量小一些。

Ciss会增加驱动功率,高频应用时,栅极驱动信号需要对Ciss充电和放电,因而会影响开关速度,降低驱动电路的输出阻抗有利于提高输出电流,提高对Ciss的充放电速度,有利于提高开关速度。

Ciss会导致VMOS在高频应用时不能被真正关断,白白消耗功率,降低PD值;Crss引起正反馈,即输;H信号会从漏极倒灌回到栅极,引起白激振荡。

Ciss、Coss、Crss的大小与源-漏极电压VDSS有关,因此有些公开的资料也将它们称为动态数(Dynamic Characteristics),不过它们几乎不受温度的影响,这给我们的电路分析带来了方便。

即使是VMOS单管也都是由不计其数的管芯单元组成的,每个管芯单元都可以视为一个微型的VMOS单管,对于一个管芯单元来说,结电容都是非常小的值,但是对于数以万计的管芯单元来说,这些结电容大致为并联关系,容量就相当可观了。

因此,管芯单元的结电容越小,—个封装内的管芯单元越少,则上述电容值就越小;电压/电流规格相同的VMOS,分布电容越小,就意味着VMOS的生产工艺越先进,能够适应的工作频率越高。

电容对高速开关信号来说都是非线性的,只有正弦波才接近线性,因此Ciss、Coss、Crss很少用于定量计算而是用于定性分析。要对分布参数对电路的影响进行定量的计算,一般采用的是更简化的方法,即栅电荷的概念。

〈烜芯微/XXW〉专业制造二极管,三极管,MOS管,桥堆等,20年,工厂直销省20%,上万家电路电器生产企业选用,专业的工程师帮您稳定好每一批产品,如果您有遇到什么需要帮助解决的,可以直接联系下方的联系号码或加QQ/微信,由我们的销售经理给您精准的报价以及产品介绍

联系号码:18923864027(同微信)

QQ:709211280