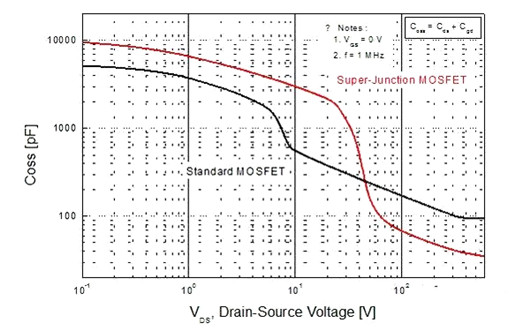

与传统平面MOSFET技术相比,超级结MOSFET可显著降低导通电阻和寄生电容。导通电阻的显著降低和寄生电容的降低虽然有助于提高效率,但也产生电压(dv/dt)和电流(di/dt)的快速开关转换,形成高频噪声和辐射EMI。

为驱动快速开关超级结MOSFET,必须了解封装和PCB布局寄生效应对开关性能的影响,以及为使用超级结所做的PCB布局调整。主要使用击穿电压为500-600V的超级结MOSFET。

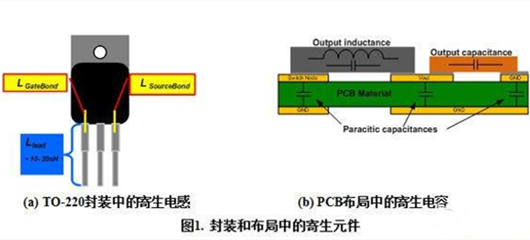

在这些电压额定值中,工业标准TO-220、TO-247、TO-3P和TO-263是应用最广泛的封装。封装对性能的影响有限,这是因为内部栅极和源极绑定线长度是固定的。只有引脚的长度可以改变,以减少封装的源极电感。

如图1(a)所示,10nH的典型引线电感看起来不大,但这些MOSFET的di/dt可轻松达到500A/μs!假定di/dt为500A/μs,10nH引线电感上的电压为VIND=5V;而10nH引线电感的关断di/dt为1,000A/μs,可产生VIND=10V的电压。

大多数应用和设计都未考虑到此附加电感也会产生电压,但这一点不可忽视。以上简单计算显示,封装的总源极电感,即绑定线和引脚电感必须降低至可接受的数值。噪声的另一个来源是布局寄生效应。

有两种可见的布局寄生效应:寄生电感和寄生电容。1cm走线的电感为6-10nH,通过在PCB顶部添加一层并在PCB底部添加GND层,可降低此电感值。另一类型是寄生电容。

图1(b)显示了布局中容性寄生效应的原理。寄生电容由两条相近走线之间或走线与另外一侧的地平面之间引起。另一种电容为器件和地平面间的电容。

PCB板两面上的两个并行走线能够增加电容,同时还能减少回路电感,从而减少电磁噪声辐射。下次设计需要超级结MOSFET时,请考虑这些布局提示。

图2:平面型MOSFET和超级结MOSFET输出电容的比较

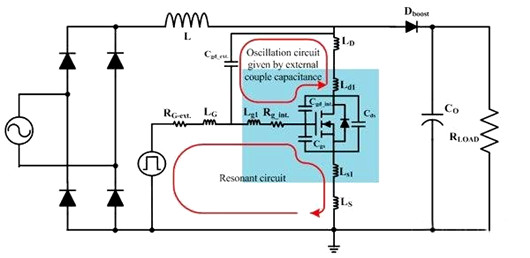

一般来说,有多个振荡电路会影响MOSFET的开关特性,包括内部和外部振荡电路。

在图3的PFC电路中,L、Co和Dboost分别是电感、输出电容和升压二极管。

Cgs、Cgd_int和Cds是功率MOSFET的寄生电容。

Ld1、Ls1和Lg1是功率MOSFET的漏极、源极和栅极邦定线以及引脚电感。

Rg_int和Rg_ext是功率MOSFET的内部栅极电阻和电路的外部栅极驱动电阻。

Cgd_ext是电路的寄生栅极-漏极电容。

LD、LS和LG是印刷电路板(PCB)的漏极、源极和栅极走线杂散电感。

当MOSFET打开或关闭时,栅极寄生振荡通过栅极-漏极电容Cgd和栅极引线电感Lg1在谐振电路内发生。

图3:包含功率MOSFET内外部寄生元件的PFC电路简图

在谐振条件(ωL=1/ωC)下,栅极和源极电压中生成的震荡电压远大于驱动电压。因谐振变化而产生的电压振荡与品质因数成正比,Q(=ωL/R=1/ωCR)。

当MOSFET关闭时,漏极寄生电感(LD+Ld1)、栅极-漏极电容Cgd和栅极引线电感Lg1网络造成栅极振荡电压。如果栅极电阻(RG-ext.+Rg_int.)极小,则Q变大。

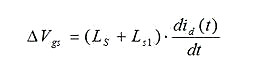

另外,LS两端的压降和Ls1源极杂散电感在栅极-源极电压中产生振荡,可用表达式(1)表示。寄生振荡可能造成栅源极击穿、不良EMI、较大开关损耗、栅极控制失效,甚至可能造成MOSFET故障。

优化电路设计,最大限度地提高超级结MOSFET的性能而又不产生负面影响非常重要。

〈烜芯微/XXW〉专业制造二极管,三极管,MOS管,桥堆等,20年,工厂直销省20%,上万家电路电器生产企业选用,专业的工程师帮您稳定好每一批产品,如果您有遇到什么需要帮助解决的,可以直接联系下方的联系号码或加QQ/微信,由我们的销售经理给您精准的报价以及产品介绍

联系号码:18923864027(同微信)

QQ:709211280