在高频开关变换器中,处理开关噪声是设计人员共同面临的挑战。特别是高边场效应晶体管导通时,低侧MOS管的体二极管需要瞬间关闭。在关闭过程中,体二极管会产生一个峰值反向恢复电流,然后突然关断。

因为有一个小但有限的寄生电感的电路,该电路将循环通过反向恢复电流,直到它消失。这将导致电压超调和SW节点产生振铃,这是非常不希望的。如果超调足够严重,低侧场效应晶体管可能再次打开或进入雪崩击穿。

另一方面,振铃可能对地产生负尖峰,而这些尖峰可能耦合到负载中的敏感电子元件上,从而导致故障。一个明显的解决方案是使用一个集成肖特基二极管的低侧场效应晶体管,如AOS SR-FET?。肖特基电路的反向恢复电流要小得多,这就减少了电路开始时的循环能量。

在系统设计过程中,降低开关噪声的最佳方法是减小寄生电感。寄生电感的来源是输入电容和开关器件之间的长轨迹。此外,驱动器件封装内的连接线也会产生不良的电感。

应遵循良好的布局实践,例如将旁路电容放置在非常接近开关器件引线的位置,尽量减少初级电流回路的面积。当开关噪声是一个主要问题时,应该使用具有低源电感的封装,如Ultra SO-8?。

然而,寄生电感在实际电路中不能完全消除。在大型复杂系统(如计算机主板)中实现理想的布局可能并不容易。在这些情况下,振铃问题的实际解决方案是通过SW节点到地的一个缓冲。在这里,我们将考虑简单的RC缓冲器,并描述如何设计一个最佳性能。

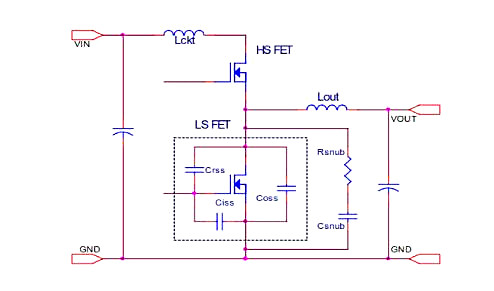

电路寄生效应

上面的原理图是同步降压转换器的简化图。所有寄生电感都集中在一起,显示为Lckt。如上所述,它们包括走线电感和封装电感。与Lck成环的寄生电容主要来自处于关断状态的低端场效应晶体管的输出电容Coss。

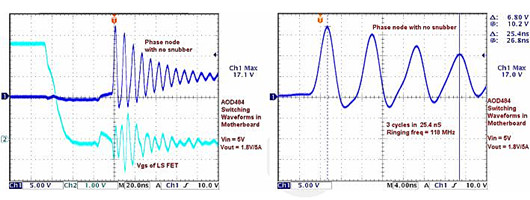

我们的目标是计算Rsnub和Csnub的值以及缓冲电阻的额定功率。将通过一个实例说明这种方法。波形是在主板上的辅助同步降压转换器中获得的,该转换器为DDR存储器供电。输入为5V,输出1.8V/5A。场效应晶体管是D-Pak中的AOD484。

下图显示了电路中没有任何缓冲器的严重振铃现象。峰值过冲是输入电压的三倍。

缓冲电阻计算

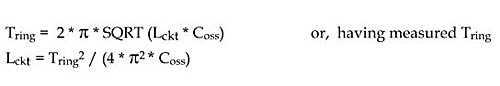

从经典电路理论可知,缓冲电阻的最佳值必须等于电路的特性阻抗。在这种情况下,电容值可以从场效应晶体管数据表中得知,但电感分布在整个印刷电路板上,很难预测。确定Lckt的一个实用方法是详细查看振铃波形并测量其频率。上方的波形显示了118 MHz或8.5 nS周期的振铃频率。

则有:

AOD484数据表给出Vds = 15V时的Coss值为142 pF。然而,Coss是Vds的函数,在低电源电压下可能显著更高。从特性曲线可以看出,在我们的5V电源下,它接近220 pF。

使用该值,Lckt计算为8.3 nH,自由振荡电路的特性阻抗为SQRT (Lckt /Coss) ? 6欧姆。这是衰减振荡所需电阻的有效值。假设电路中已经存在一些电阻,我们可以选择5欧姆作为缓冲电阻。(SQRT是开根号的意思)

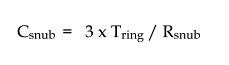

缓冲电容计算

缓冲电容值是一个权衡。较大的电容器将提供过阻尼并减少振荡次数。但是电容器还存储CV*CV/2的能量,并在每个周期消耗它,这对效率有影响。一个有用的参数是Rsnub x Csnub时间常数,表示为振铃周期字符串的倍数。标准做法是使用3或更高的倍数。

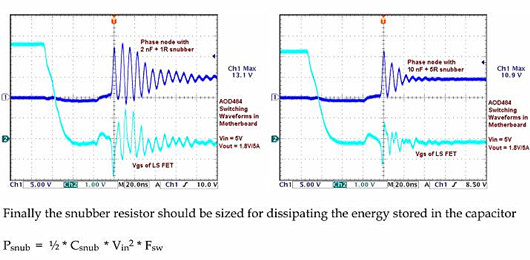

在我们的例子中,Csnub的最小值是4.7 nF。在主板中,选择10 nF的值来提供额外的阻尼。由于输入仅为5V,这不会导致缓冲器过度损耗。下图显示了较低值缓冲器(2 nF + 1欧姆)的效果。将它与右侧的缓冲器进行比较,优化后的缓冲器为10纳法+ 5欧姆。

最后,缓冲电阻的大小应能耗散存储在电容中的能量。

请记住,Fsw是转换器的开关频率,而不是振铃频率。在我们的例子中,开关频率为300Hz,功率损耗为37mW,不到输出功率的0.5%。

结论

值得重复的是,电路中的寄生电感分布在整个印刷电路板上,包括封装电感。虽然缓冲器元件是假设它们的有效值来计算的,但是没有办法将它们物理地放入电路中以提供理想的阻尼。减少过冲和振铃的最佳方法是通过良好的布局实践将电路中不良电感降至最低。选择合适的低电感封装低端场效应晶体管和/或集成肖特基体二极管将带来额外的好处。

〈烜芯微/XXW〉专业制造二极管,三极管,MOS管,桥堆等,20年,工厂直销省20%,上万家电路电器生产企业选用,专业的工程师帮您稳定好每一批产品,如果您有遇到什么需要帮助解决的,可以直接联系下方的联系号码或加QQ/微信,由我们的销售经理给您精准的报价以及产品介绍

联系号码:18923864027(同微信)

QQ:709211280