在28nm以下,由于最大器件长度限制,模拟设计人员经常要对多个短长度的MOSFET串联来创建长沟道的器件。这些串联连接的器件通常被称为堆叠MOSFET或堆叠器件。

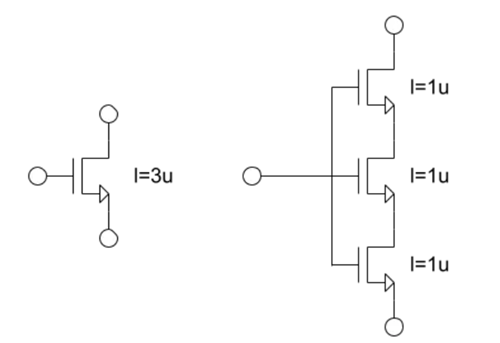

例如,将三个1μm的MOSFET串联堆叠,可创建一个沟道长度为3μm的有效器件(图1)。

图1:将三个MOSFET串联堆叠,可提供3μm的沟道长度。

堆叠MOSFET在现代模拟设计中非常常见,但并不是没有问题。其主要问题是电容增加以及面积更大。电容增加很大程度上是由于器件周围的互连增加。

总栅极面积和总栅极电容与非堆叠等效电路相似,但在互连线上有额外的寄生电容。与单个长沟道器件相比,堆叠器件的物理分离增加了总设计面积。

当在电路中使用堆叠MOSFET时,版图质量变得比平常更重要。不良的版图设计会显著增加寄生电容和设计面积,并可能使电路无法满足期望的性能特性。

版图设计工程师必须非常小心地设计这些器件的版图。大多数从事于这些较小工艺节点的设计人员都经历过版图前仿真和版图后仿真非常不同的情况。通常,这归因于堆叠器件上所存在的互连寄生效应。

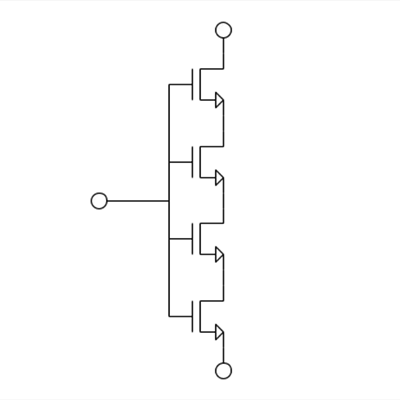

下面来看看几种实现堆叠MOSFET高质量版图的方法。图2中的子电路显示了将四个NMOS MOSFET堆叠在一起而创建一个长沟道器件。

图2:将四个MOSFET堆叠,可创建一个长沟道电路。

在这个电路中可以看到,所有的栅极引脚都是相互连接的(所有四个整体连接也是如此),也可以看到,所有的MOSFET都是通过将一个器件的漏极与下一个器件的源极串联起来而连接在一起。

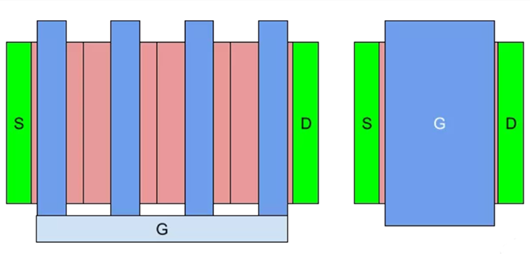

在这种情况下,由于每个器件都是简单的单指MOSFET,因此可以使用简单的扩散分配版图模式来设计这种结构的版图。

图3:将左边的简单堆叠情况与右边的等效长沟道器件进行比较。

简单堆叠情况的版图如图3左边所示,可以看到它几乎没有额外的互连,因为等效的长沟道器件(右边)也需要一个多晶硅触点。在这种情况下,面积不利显著,但这是不可避免的,并且由多晶硅最小间距规则所决定。

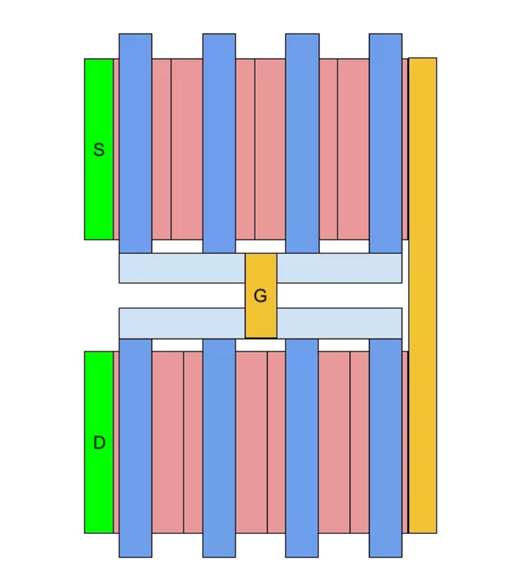

这种方法的另一个问题是,非常长的有效器件可能导致非常长的扩散分配链路。然而,可以将长链折叠成多行,如图4所示。但是,其代价是这增加了额外的互连,并进一步增加了堆叠器件的电容。

图4:可以将长链折叠成多行。

〈烜芯微/XXW〉专业制造二极管,三极管,MOS管,桥堆等,20年,工厂直销省20%,上万家电路电器生产企业选用,专业的工程师帮您稳定好每一批产品,如果您有遇到什么需要帮助解决的,可以直接联系下方的联系号码或加QQ/微信,由我们的销售经理给您精准的报价以及产品介绍

联系号码:18923864027(同微信)

QQ:709211280