运放失配设计

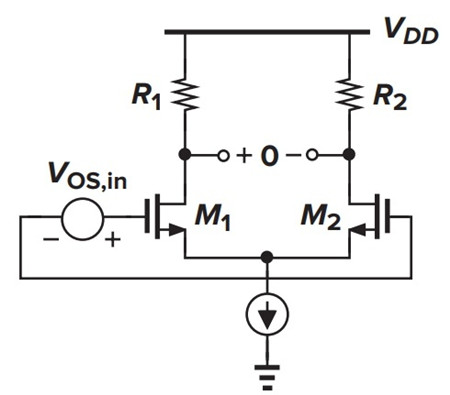

图1 电阻负载运放

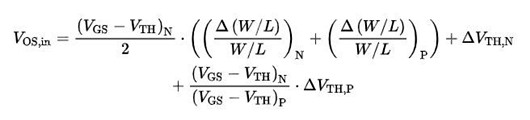

根据拉扎维《模拟CMOS集成电路设计》中14.2.1节的推导,电阻负载的运放的直流失调可以表示为式1:

由式(1)可知:

负载电阻失配与晶体管尺寸失配对失调电压的影响随着静态工作点过驱动电压增大而增大;

阈值电压失配直接折合到输入。

因此,在电路设计时,应该设计运放的输入对管具有更小的过驱动电压以减小失调。

电流镜失配设计

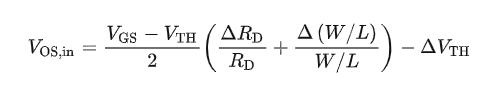

根据拉扎维《模拟CMOS集成电路设计》中14.2.1节的推导,电流镜的电流失配用平均电流值归一化后可表示为式(2):

这个结果表示,为了使电流失配最小,必须使过驱动电压达到最大,这与式(1)结论是相反的,这是因为在平方律公式中,随着VGS-VTH的增加,阈值电压的失配对器件电流的影响越来越小。

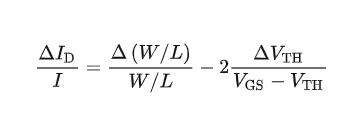

电流源负载的运放失配设计

对于电流源负载的运放,负载电流源会存在式(2)所示的的电流失配ΔID,其等效到运放的失调电压为ΔID/gm,对于给定的电流,gm=2ID/(VGS-VTH),即负载电流源的失配引起的运放输入失调会随着输入对管过驱动电压的增大而增大。

图2 电流镜负载运放

同时考虑运放输入对管和负载电流镜晶体管的失配后,如图2所示运放的输入失调电压可表示为式(3):

式(3)可知,在设计运放时,在给定电流下,应该使输入对管具有更小的过驱动电压,而使负载电流源晶体管具有更大的过驱动电压,以此获得更小的运放输入失调。

〈烜芯微/XXW〉专业制造二极管,三极管,MOS管,桥堆等,20年,工厂直销省20%,上万家电路电器生产企业选用,专业的工程师帮您稳定好每一批产品,如果您有遇到什么需要帮助解决的,可以直接联系下方的联系号码或加QQ/微信,由我们的销售经理给您精准的报价以及产品介绍

联系号码:18923864027(同微信)

QQ:709211280