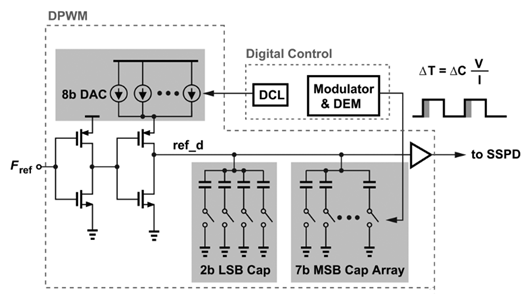

CMOS延时单元的设计,如下图所示,8bitDAC和9bit电容阵列一起控制输出脉冲的形状,输出信号的时钟沿延时一般都是通过改变反相器的电流和输出电容来改变的。

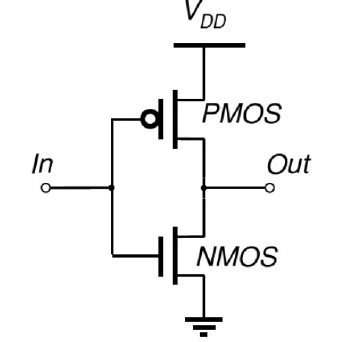

如下图所示的反相器,其传输延时是由NMOS和PMOS的等效电阻对负载电容Cload(一般指下一级输入电容)充放电所消耗的时间决定的。

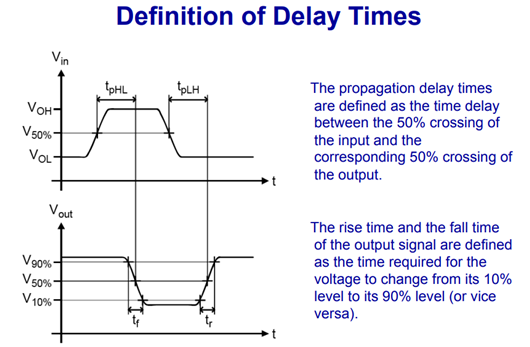

关于反相器中的一些延时定义如下:

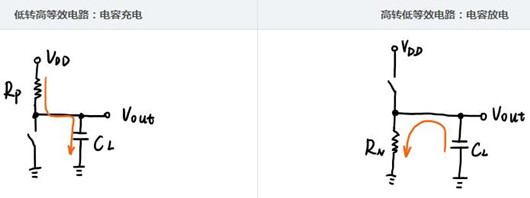

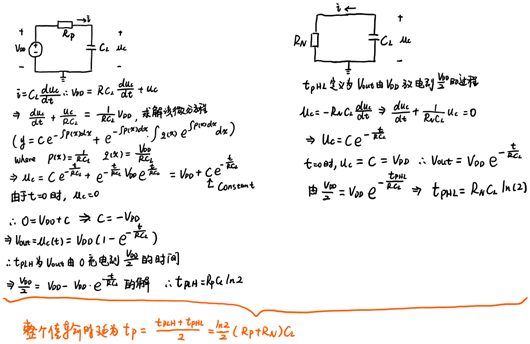

定义tpLH为Vout由低电平翻转至高电平的传输延时(以50%为参考),此时的CMOS反相器可等效为下表左图所示的电路。

定义tpHL为Vout由高电平至低电平翻转的传输延时,此时的CMOS反相器可等效为下表右图所示的电路。统称为propagation delay。tf和tr分别表示下降延时和上升延时,这里暂时不作讨论。

从电压角度列方程,传输延时的推导如下:

从电流角度看的话,就直接是RC电流充放电了,可以直观理解:电流越大,延时越小,电流越小,延时越大。

〈烜芯微/XXW〉专业制造二极管,三极管,MOS管,桥堆等,20年,工厂直销省20%,上万家电路电器生产企业选用,专业的工程师帮您稳定好每一批产品,如果您有遇到什么需要帮助解决的,可以直接联系下方的联系号码或加QQ/微信,由我们的销售经理给您精准的报价以及产品介绍

联系号码:18923864027(同微信)

QQ:709211280