针对功耗来源,提出低功耗设计常用方法。

降低电源电压;

减小负载电容;

减少MOS管数量;

减小连线电容

减少电荷分享的影响(对动态电路)

节点开关活动因子的影响;

从算法和体系结构角度优化;

选择具有低功耗功能器件;

时钟门控;

提高工艺

使用新型低功耗器件和材料,减少晶体管尺寸,如从28nm到16nm等。

时钟门控技术

频繁的信号翻转会造成很大的短路电流,以及对负载电容进行频繁的充放电,即增大所谓的内部功耗(Internal Power)和切换功耗(Switch Power)。

在现代数字集成电路设计中,时钟信号作为数据传输的基准,对于同步数字系统的功能、性能和稳定性起决定性的作用。

通常时钟信号有高扇出,高频率,路径长的特点,在当前的高端SoC系统中,时钟频率已经超过1GHz,所以时钟树上消耗的功耗十分的可观,大约占到系统总功耗的30%到40%。同时时钟信号连接时序单元,如寄存器和锁存器,所以这些时序单元上同样消耗了不可忽视的动态功耗。

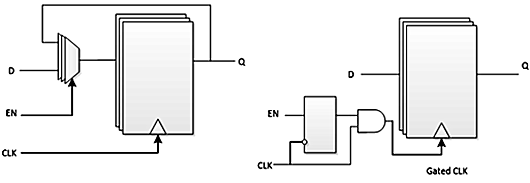

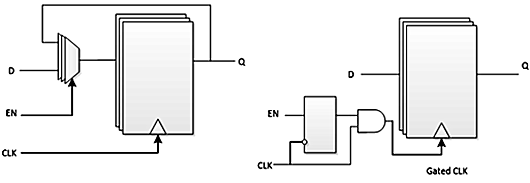

门控时钟技术作为一项传统的降低动态功耗的技术被广泛应用于现代数字集成电路设计中,即用一个控制信号控制时钟的开启和关闭,在模块不工作时关闭时钟,在需要工作的时候,打开时钟,从而通过降低触发器总的翻转率达到降低功耗的目的,其特点为实现简单,并且十分有效。

通过用EN信号控制时钟信号的开关,在EN信号无效时,寄存器的时钟端将保持一个定值,D端的数值将不能传到Q端。

多电压域技术

芯片的动态功耗正比于电压值的平方,静态功耗正比于电压值,因此芯片的电压域管理策略对芯片的功耗影响很大。

多电压域技术是按照芯片功能和应用需要,将不同的逻辑模块放置在不同的电压域中,这些电压域由电源管理模块分别独立供电,使得不同的逻辑模块可以在不同的电压下工作。

例如,某一段时间内,某些性能要求不高的模块可位于低电压域中,而性能要求较高模块的供电电压相应较高,且多电压域技术也是动态电压频率缩放(Dynamic Voltage and Frequency Scaling , DVFS)、静态电压缩放(Static Voltage Scaling, SVS)、自适应电压缩放(Adaptive Voltage Scaling, AVS)设计的基础。

电路采用多电压域技术会给设计带来一些的新的挑战:

信号在不同电压域之间传递,需要插入电平转换器(Level Shifter)实现电平转换。

由于芯片各个模块会工作在多种电压下,因此在各种电压下的时序要求都要满足,加大了静态时序分析(Static Timing Analysis ,STA)的复杂度。

电源网格(Power grids)的布局规划、模块接口单元的电源布线等都变得更复杂。

板级上需要更多电压调节器来提供各种不同电压,增加板级设计的复杂度。

由于各个模块电压不同,模块间上电/下电顺序也需要仔细设计以避免电路出现死锁。

电源门控技术

随着工艺技术的发展,由漏电流所产生的功耗所占的总功耗比例越来越大。对于诸如手机的手持移动设备中的SoC芯片,休眠模式下漏电流功耗的大小是设计者在设计时必须考虑的设计因素。

对于希望在休眠模式下尽量节省功耗的设计来说,最好的办法是,将处于休眠模式状态的模块的供电电源关断而保持其它模块的正常供电,这种技术叫电源门控技术。

电源门控技术与时钟门控技术相比,时钟门控降低的仅仅是电路的动态功耗,而电源门控不仅降低动态功耗,而且降低静态功耗。

时钟门控技术不影响设计电路的功能,也无须修改RTL(Register Transfer Level)代码,它在设计和实现上可以是对设计者透明的,而电源门控技术影响各模块之间的相互连接,安全进入和退出电源门控模式会增加很多额外的操作。

电源门控一般有两种方法来实现:

外部电源门控(external power gating)。实现电源门控最基本的方法,适于消耗漏电功耗较少但关断时间较长的设计。

举个例子,一个SoC系统在板极上有CPU的专用电源,这个电源只提供电压给CPU。外部电源门控技术就是,可以关闭这个电源以使CPU在非活动状态时漏电功耗减小到零。但这种做法也需要最长的时间对电源门控的模块进行供电和数据的重新加载。

内部电源门控(on-chip power gating)。内部电源门控是指在芯片内部用一些专门的逻辑单元如电源门控单元来控制所选模块的供电情况。

外部电源门控技术与内部电源门控技术均能实现将电压域中电压关断从而最大限度地减小漏电功耗的目的,但在物理实现过程中,内部电源门控技术要复杂得多。

器件低功耗

SOC系统中各个器件选型时,选择具备低功耗功能器件,但器件无业务工作需求时,可以进入低功耗状态。

RTL级优化

不同的RTL(RegisterTransferLevel,寄存器传输级)代码,也会产生不同的功耗,而且RTL代码的影响比软件代码产生的影响可能还要大。因为,RTL代码最终会实现为电路。电路的风格和结构会对功耗产生相当重要的影响。

RTL级代码优化主要包括:

①对于CPU来说,有效的标准功耗管理有睡眠模式和部分未工作模块掉电。

②硬件结构的优化包括能降低工作电压Vdd的并行处理、流水线处理以及二者的混合处理。

③降低寄存电容C的片内存储器memory模块划分。

④降低活动因子a的信号门控、减少glitch(毛刺)的传播长度、Glitch活动最小化、FSM(有限状态机)状态译码的优化等。

⑤由硬件实现的算法级的功耗优化有:流水线和并行处理、Retiming(时序重定)、Unfolding(程序或算法的展开)、Folding(程序或算法的折叠)等等基本方法以及其组合。

后端综合与布线优化

SoC的功耗与寄生电容的充放电有很大的关系,作为后端综合与布线,同样也可采取一些措施来减少寄存器电容。能够优化电路,减少操作(电路的操作),选择节能的单元库,修改信号的相关关系,再次综合减少毛刺的产生概率。

实际上,这个部分与使用的工具相关。与软件部分有相同之处,后端综合与布线同软件的编译差不多。软件编译的结果是产生可执行的机器代码;而RTL的综合与布线是把RTL代码编译成真实的电路。

但是,后端综合与布线优化比较编译优化有更好的效果。这是因为一段RTL代码所对应的电路是能够有多种形式的;同时现有些编译器会根据设计者提供的波形,智能地修改电路(前提是最终电路的效果还是一样的),编译器就会实行相关的优化。

但是后端综合的优化与RTL级代码优化和时钟控制相比,同样的RTL级与时钟优化所产生的影响要远大于用编译工具所产生的影响。

功耗的精确计算

后端综合与布线工具不但能够根据基本单元提供的功耗参数实行优化,还能够根据这些参数估算出整个SoC的功耗。正因为有这样一些工具,使我们能够精确地知道我们所设计的是否达到设计要求。

万一设计功耗不符合总体要求,则可能要求从系统级到物理综合布线都要做出检查与分析,做出可能的改进,尽可能地减少功耗以达到设计要求。

自适应阈值电压调节技术

自适应阈值电压调节技术(Adaptive Voltage Scaling,AVS)技术的基本思想是将PVT因素对电路的影响归为延时特性的变化,在电路中加入监测单元监测延时信息,根据电路延时调节电压,降低设计阶段预留的电压余量,从而使芯片处于最佳能效状态,降低功耗。

AVS技术利用硬件调节电压,无需软件执行,调节效率高且不影响系统性能;它可以降低工艺偏差、温度及老化对芯片的影响,提高芯片的产量与质量,还可以降低芯片电源IR-drop的影响;另外它只需在SoC中添加少量监测电路即可实现,额外的面积及功耗消耗都不大。

AVS的监控单元有两种常用的方法。

一种是环形振荡器监控的方法,环形振荡器的监控方法是在芯片中放置工作在相同环境(工艺、电压、温度相同)下的环形振荡器,通过环形振荡器的振荡频率可以知道在当前温度、工艺环境下频率与电压的关系,从而达到对整个芯片的工作环境进行监控的目的。

另一种是关键路径监控方法,通过可配置的延迟链来复制关键路径,使可配置的延迟链的延迟长度和关键路径相同,这些可配置的延迟链包含反相器、与非门和线延迟等等。一个典型的关键路径监控示意图如图所示。其中时间数字转换器(Time Digitizer),是通过传输门和触发器组成的。

〈烜芯微/XXW〉专业制造二极管,三极管,MOS管,桥堆等,20年,工厂直销省20%,上万家电路电器生产企业选用,专业的工程师帮您稳定好每一批产品,如果您有遇到什么需要帮助解决的,可以直接联系下方的联系号码或加QQ/微信,由我们的销售经理给您精准的报价以及产品介绍

联系号码:18923864027(同微信)

QQ:709211280