所谓集成电路可靠性是指半导体集成电路在一定的工作条件下(指一定的温度、湿度、机械振动、电压等),在一定的时间内能够完成规定作用的几率。集成电路可靠性问题的提出是与电子信息产业迅速发展的下列三个特点分不开的。

1.电子信息系统产品的复杂程度不断增长

电子信息系统产品复杂程度的重要标志是所需元件的数量越来越多。如美国轰炸机上的无线电设备情况是:1921年前飞机上还没有无线电设备,1940年飞机上的电子设备只有一千多个,1950年B-47飞机上的电子设备发展到2万多个,1955年B-52飞机上的电子设备发展到5万多个,1960年B-58飞机上的电子设备发展到9万多个;一般制导系统上的计算机部分就有10万多个电子元器件。

一般来说,电子系统所采用的电子元器件个数越多,其可靠性问题就越严重,对于相关性很强的电子系统来说,其系统可靠性为所用电子元器件可靠性的乘积。假设元器件的可靠性均为99.5%,则采用100个元器件组成系统的可靠度仅为60%。若30万个元器件组成系统,为了确保系统可靠度为95%,则要求每个元器件的可靠度为99.9999%以上。现代大型电子系统的电子元器件数量达百万个以上,对电子元器件可靠性的要求则更高。

2.电子系统设备的使用环境日益严酷

现代电子系统设备的使用环境从实验室到野外、从陆地到海洋、从高空到太空,还有使用在热带、南北极等地的。各种不同地方的电子设备需要经受不同的环境条件,如军用武器装备中的强振动和加速度、外部空间的粒子辐射和核武器的核辐射等。一般来说,使用条件越严酷,系统失效的可能性就越大,对可靠性的要求也越高。

3.电子系统的组装密度不断提高

为了减小电子系统的体积和重量,除了采用更高集成度的集成电路外,还需要采用多芯片组件(MCM)的方式进行二次集成。组装密度的提高,使得系统内部的环境温度迅速提高,加速电子元器件的老化过程,高速信号之间的串扰也越来越严重,所以对可靠性的要求也进一步提高。

一、集成电路可靠性

集成电路可靠性通常用失效率进行量度。瞬时失效率λ(t)定义为某个相当短的时间间隔Δt内,失效的器件数Nt与这段时间内工作的器件总数N(t)和时间间隔Δt的乘积之比,即

λ(t)=Nt/N(t)Δt

λ(t)采用非特(1非特=0.0001 %/1000小时=10^-9/小时)来度量。瞬时失效率简称为失效率,用于描述在各个时刻仍在正常工作的器件失效的可能性。

集成电路的可靠性效应可以分为6类:静电效应、热效应、二次击穿效应、闩锁效应、化学效应和辐射效应。

当带有静电荷的物体与非带电导体接触时,带电导体会通过非带电导体放电,即静电放电。如果带电体是通过集成电路进行放电,就会对器件带来损伤,导致器件失效,即静电效应。带电人体对集成电路的静电效应是最主要的。

集成电路工作时所消耗的功率要通过发热的形式耗散出去,如果集成电路的散热能力有限,则所消耗的功率会引起集成电路内部温度的上升,如果集成电路的工作环境温度过高或是由于在高寒地带不连续工作等原因引起温度交替变化,也会在集成电路内部产生高温应力或温度循环应力,从而引起集成电路失效,即热效应。

二次击穿是一种典型的集成电路体内失效,是严重威胁功率集成电路和高压集成电路安全使用的主要失效模式。二次击穿与雪崩击穿有本质的区别,二次击穿是不可逆的,具有破坏性,器件在二次击穿状态下停留时间过长或经受多次二次击穿,其特性将显著恶化,可能会被突然烧毁。

CMOS集成电路具有一种独特的闩锁(Latch Up)失效,不仅对其可靠性造成了严重威胁,而且成为进一步提高其集成度和性能指标的主要障碍。CMOS集成电路的基本逻辑单元是由一个PMOS晶体管和一个NMOS晶体管以互补形式连接构成。为了实现NMOS和PMOS的隔离,必须在n型衬底内加进一个p型区(称为p阱)或者在p型衬底内加进一个n型区(称为n阱)。由于NMOS和PMOS都做成增强型,所以通常在未接输入信号时,它们都处于截止状态,正电源端和负电源端之间几乎没有电流流过。但是,在测试和使用过程中,有时器件引出端(包括输出端、输入端和电源端等)受到外来的电压或电流信号的触发,正电源端和负电源端会出现很大的导通电流。该电流一旦开始流动、即使除去外来触发信号也不会中断,只有关断电源或将电源电压降到某个值以下才能解除这个电流。这个现象就是CMOS集成电路闩锁效应。

集成电路在储存、保管和使用过程中,特别是装有器件的电子设备在沿海、海上和亚热带地区使用时,会遇到高温潮湿、酸雨和盐雾环境条件。在这种条件下,器件有可能因电化学反应遭到腐蚀而失效。一方面,器件的外引线和管壳可能直接被腐蚀,这种现象以柯伐合金引线最为显著;另一方面,由于管壳的密封性缺陷或封装材料本身的吸气性(对塑料封装),水汽可能会渗入管壳内部,使芯片表面的铝金属化布线被腐蚀或芯片电性能劣化,即化学效应。

随着空间技术、核技术和战略武器技术的发展,各种电子设备已经广泛用于人造卫星、宇宙飞船、运载火箭、远程导弹和核武器控制系统中。构成电子设备的电子元器件不可避免地要处于空间辐射和核辐射等强辐射应用环境之中,辐射作用会对元器件性能造成不同程度的破坏,进而使整个电子设备发生故障。例如,装在导弹上的集成电路因受到辐照而失效,就会使弹上计算机系统发生逻辑误差,结果使导弹失控而迷失方向或者过早爆炸,甚至不能爆炸,这种失效应被称为辐射效应。

二、集成电路设计中提高可靠性的措施

集成电路的电路设计中提高可靠性的基本原则是把对器件的要求与具体工艺情况结合起来,因此熟悉工艺特点是搞好设计的基础。在电路设计中可以采取以下一些措施来提高集成电路的可靠性:

(1)明确电路技术指标和使用环境。

(2)减小面积和复杂性。在满足功能要求的基础上简化电路以尽量减少总面积和复杂性,减少接点数目(如减少双极集成电路隔离岛数目等)。面积减小能使缺陷减少,从而使可靠性提高。

(3)对于电路器件给予一定的容差,即按最坏情况进行设计,这也叫容差设计。

(4)在同样参数指标情况下,尽量降低电路的功耗(例如工作电流要选择恰当等),以降低电路工作时的结温,提高可靠性;当最大电流Imax≤2×10^5A/cm2 时,还有利于防止电迁移。

(5)必要时要考虑元件的冗余设计,即增加并联或串联元件以确保可靠性,这一点常在部件或整机设计中考虑。

(6)在某些电路中加设保护电路,如集成稳压器中加过压保护、过流保护,集成运放输出级加过流保护电路,在高温度稳定的电路中加温度补偿电路,输入端加输入保护电路等。下面重点介绍CMOS集成电路中输入端防静电击穿(ESD)的输入保护网络。

1.二极管和电阻双层ESD保护结构

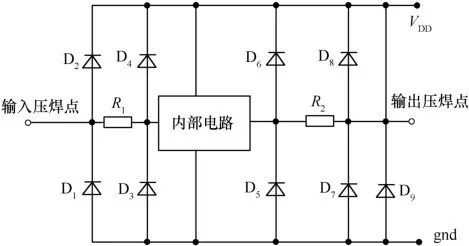

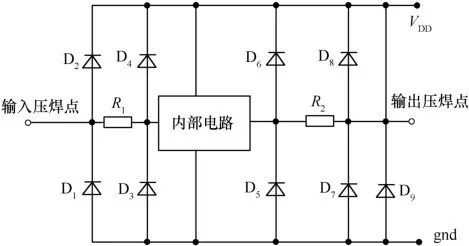

采用二极管和电阻双层保护结构对ESD进行钳位和滤除放电电荷是一种常用的保护电路技术,早期的NMOS电路都采用这种保护技术,目前的一些小规模CMOS电路也采用这种ESD结构。简单的二极管在正偏时可以用来作为钳位单元抑制ESD,其开启电阻(Ron)比较低,约为10Ω,触发电压也比较低。另一方面,二极管在反偏时,其作为钳位单元的特性较差,由于此时其Ron很高,约为100Ω,从而导致很大的能量消耗。这种ESD结构设计和工艺条件都比较简单,是比较普遍的ESD保护电路的形式。对于有抗静电要求的微米级CMOS集成电路,可以采用如图1所示的保护电路,D2、D4、D6和D8是p+扩散电阻的分布二极管。D1、D3、D5、D7和D9是由p-n+结形成的二极管。

图1 基本的二极管和电阻双层ESD保护结构

利用二极管钳位和RC低通滤波可以使端口处出现的ESD电荷脉冲通过保护网络旁路,避免进入到电路内部,同时对端口处出现的其他干扰也能滤除。

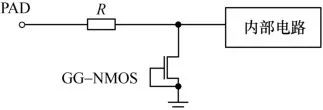

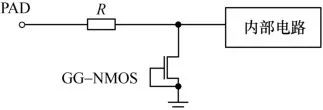

2.GG-NMOSESD保护结构

在CMOS集成电路技术中,GG-NMOS(栅、源、衬接地的NMOS)ESD保护结构是目前应用最广泛的ESD保护措施,主要应用于微米及亚微米CMOS集成电路的ESD保护,图2为典型的GG-NMOS ESD保护结构。GG-NMOS ESD保护结构是利用Snapback特性来钳位瞬态高压和分流,具有低钳位电压和低开启电阻的特点,而二极管ESD保护结构的开启电阻较大。当正脉冲(ESD)加在漏结上(n+/p),该结反偏,器件进入高阻抗状态,直到达到击穿电压为止。由于处于高场状态,在耗尽区产生电子、空穴对,电子被漏接触电极收集,而空穴被衬底接触电极所收集。相对于接地的源结,衬底的局部电势不断增加。当局部电势增加到足以使源极—衬底结正偏时,电子就从源区注入漏区。

图2 GG-NMOSESD保护结构

3.寄生PNP和NPNESD保护结构

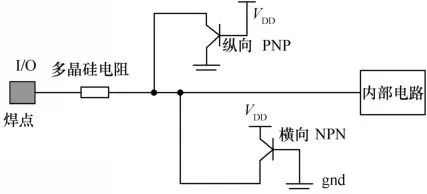

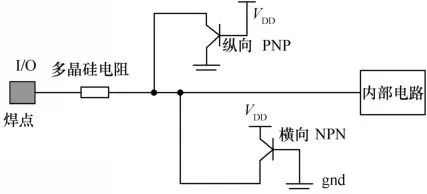

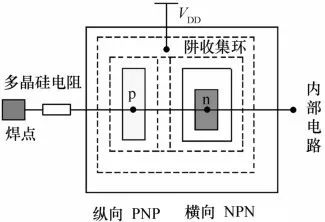

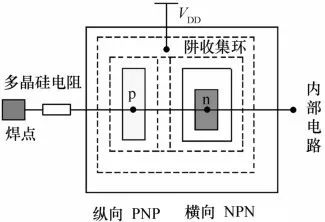

全寄生的双极性PNP和NPN晶体管ESD保护网络,能有效避免PN结钳位或MOS管钳位结构产生的钳位电流中的少数载流子向内部电路区扩散,其结构如图3所示。

图3 寄生PNP和NPN ESD保护结构

在这种ESD保护电路中,多晶硅电阻吸收了大部分的ESD能量。这种保护电路实际上是用p+和n+扩散区形成的,其钳位方式是采用PN结钳位的。由p+扩散区形成的二极管与n阱构成了寄生的垂直PNP晶体管。阱收集环包围了n区和衬底,收集了大部分ESD放电注入衬底中的少数载流子,并且该环作为横向NPN晶体管的集电极。该保护电路在静电放电过程中,可以使到内部电路去的连线钳位在VDD和VSS(地)电位之间。图4是基于n阱CMOS工艺的寄生PNP和NPN ESD保护结构版图。

图4 基于n阱CMOS工艺的寄生PNP和NPN ESD保护结构版图

4.SCRESD保护结构

采用寄生的横向PNPN结构(SCR)的ESD保护结构是目前最有效使用最广泛的一种ESD保护结构,具有大电流吸入/输出、低的接通阻抗等特性,并具有较大的热耗散体积。但是SCR器件需要有一个高触发电压,同时为了执行保护功能,该触发电压又必须小于输入缓冲器或者输出驱动器的损伤电压。据实验表明,在具有LDD和硅扩散1μm CMOS工艺制作的、阴阳极间距为6μm的寄生横向SCR器件的触发电压为50V,所以不能采用单独的寄生横向SCR作为唯一的ESD保护器。为了提供更宽范围的ESD保护,早期的SCR四层结构保护电路中,大都采用了诸如电阻和二极管等次级保护元件。也有研究者为了减少次级保护元件,采用两种方法,降低寄生横向的SCR触发电压。一种办法是在横向SCR内集成一个低击穿电压的短沟道NMOS晶体管,形成“LVTSCR”的结构,该结构的触发电压一般为10~15V,但是要将这个NMOS晶体管和横向SCR结合在一起比较困难。另外一种解决办法,为了获得较低的触发电压而增加了一块“NLCS”掩模,用来完成横向SCR内深处的场注入。这种办法得到的最小触发电压为9V。这个办法的缺点是要增加掩模和工艺步骤,没有广泛应用。

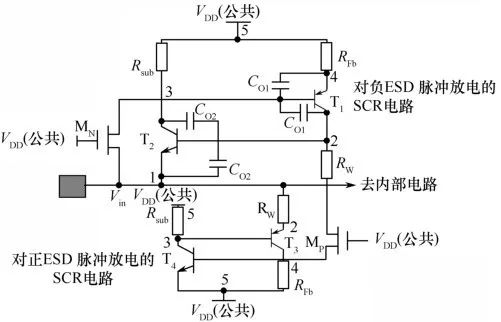

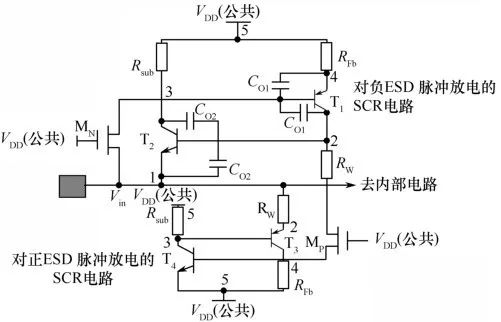

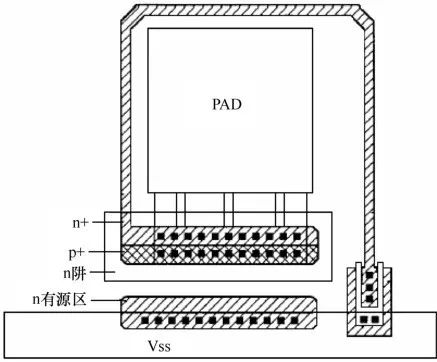

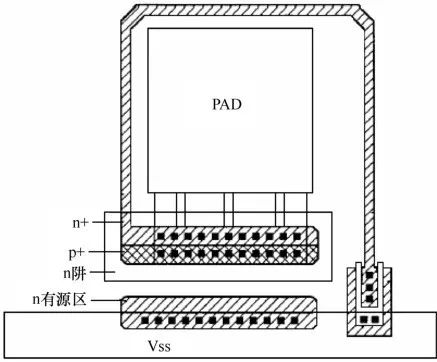

目前,双寄生横向SCR结构的ESD保护电路被广泛采用,如图5所示。在这个ESD保护电路中,一个寄生横向SCR结构安排为对正的ESD脉冲放电,另一个则安排对负的ESD脉冲放电。两个SCR都具有较低的触发电压。在这种ESD保护电路中,不存在PN结或器件的击穿。这就避免了数次ESD瞬变之后,由于器件或结击穿引起性能退化。这种保护电路具有小的版图尺寸、低输入电容和低接通电阻。比较理想的满足了CMOS电路芯片上ESD保护电路的设计要求。图6为其中一种SCRESD保护电路的版图。

图5 双寄生横向SCRESD保护结构

图6 SCRESD保护结构版图

三、集成电路的版图设计中提高可靠性的措施

版图设计的好坏直接影响电路生产的成品率及可靠性。好的设计不但本身很少带来不可靠因素,而且对于工艺上难以避免的问题,也能预防或减弱其影响。

根据使用的温度范围(军用-55~125℃,民用-25~85℃)及其他可靠性要求,版图设计需要考虑电性能和热性能。由电参数要求及工艺水平来确定元件的结构、尺寸,再考虑寄生效应、散热等问题,从而最后确定整个电路的布局和布线。可靠性设计的内容很多,下面介绍一些主要措施。

1.关于金属化层布线

大量的失效分析表明,因金属化层(目前一般是Al层)通过针孔和衬底短路,且Al膜布线开路造成的失效不可忽视,所以必须在设计布线时采取预防措施。例如尽量减少Al条覆盖面积,采用最短Al条,并尽量将Al条布在厚氧化层(厚氧化层寄生电容也小)上以减少针孔短路的可能。

防止Al条开路的主要方法是尽量少的通过氧化层台阶。如果必须跨过台阶,则采取减少台阶高度和坡度的办法。

为防止Al条电流密度过大造成的电迁移失效,要求设计时通过Al条的电流密度J<2×10^5A/cm2,Al条要有一定的宽度和厚度。

对于多层金属布线,版图设计中布线层数及层与层之间通道应尽可能少。

2.版图设计中的热分布问题

据推测,芯片温度每提高25℃失效率约增加一倍,所以要尽量降低芯片温度以降低失效率。为防止结温过高,功率较大的管子面积要设计得足够大,而发射区有效边长仍由最大电流确定。在整个芯片上发热元件的布局分布要均匀,不使热量过分集中在一角。在元件的布局上,还应将容易受温度影响的元件远离发热元件布置。在必须匹配的电路中,可把对应的元件并排配置或轴对称配置,以避免光刻错位和扩散不匀。要注意电源线和地线的位置,这些布线不能太长。

3.其他措施

(1)元件尺寸的选择要适当。应考虑功率密度、寄生效应、制版光刻误差、横向扩散及扩散容差等因素,Al条应覆盖欧姆接触孔并留一定余量。

(2)保证电路参数的要求:多发射极晶体管的长脖子区不宜太长,因为太长会导致fT下降;避免在输出线上做扩散“地”道;外延层电阻岛上接电源的欧姆接触孔要扩n+。

此外,对于CMOS集成电路,为提高其抗闩锁能力可在版图设计上采取以下措施:①合理布置电源接触孔,减小横向电流密度和横向电阻;②采用接衬底的环形VDD电源线(p阱),并尽可能将衬底背面接VDD;③增加电源VDD和VSS(GND)接触孔,并加大接触面积;④对每一个接VDD的孔都要在相邻的阱中配以对应的VSS(GND)接触孔,以便增加并行的电流通路;⑤尽量使VDD和VSS的接触孔的长边相互平行;⑥接VDD的孔尽可能安排得离阱远一些;⑦接VSS的孔要尽可能安排在p阱的所有边上。

电话:18923864027(同微信)

QQ:709211280

〈烜芯微/XXW〉专业制造二极管,三极管,MOS管,桥堆等,20年,工厂直销省20%,上万家电路电器生产企业选用,专业的工程师帮您稳定好每一批产品,如果您有遇到什么需要帮助解决的,可以直接联系下方的联系号码或加QQ/微信,由我们的销售经理给您精准的报价以及产品介绍