众所周知,现场可编程门阵列(FPGA)是一种现场可编程专用集成电路,其速度快、功耗低,特别适用于复杂系统的设计,如今,FPGA器件已广泛应用于通信、自动控制、信息处理等诸多领域,越来越多的电子设计人员在使用FPGA。Cyclone系列芯片中的EP1C3T144C8是ALTERA公司推出的一款低价格、片上资源丰富、高容量的FPGA,在实际应用中被广泛的采用。本文主要介绍的是基于EP1C3T144C8开发板设计。

1.硬件电路整体结构

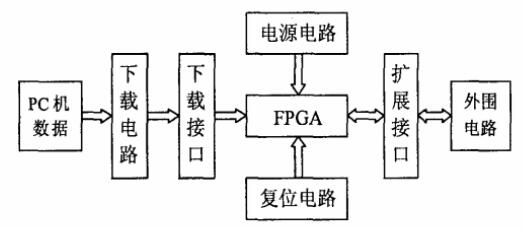

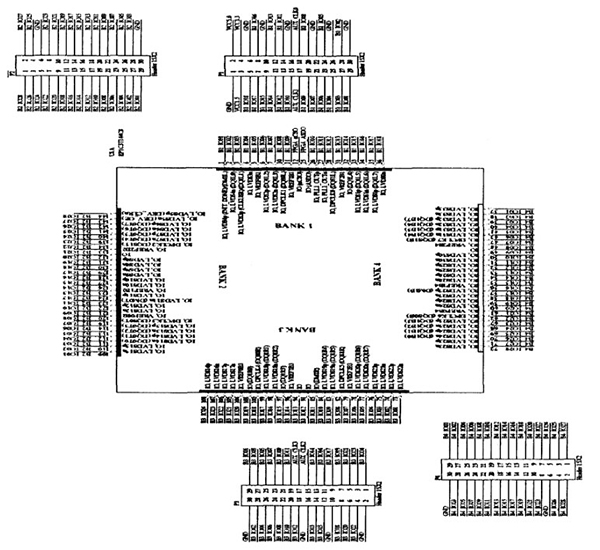

本设计的开发板电路包括6个部分:下载电路、下载接口、FPGA、电源电路、和扩展接口。其电路结构框图如图1所示:

图1 电路结构框图

2.主芯片EP1C3T144C8

本设计选用Altera公司的Cyclone系列芯片,芯片型号为EP1C3T144C8,因为该芯片是Altera公司推出的低价格、高容量的FPGA,其以较低的价格、优良的特性及丰富的片上资源在实际应用中被广泛的采用。该芯片采用1.5V内核电压,0.33 μmSRAM工艺,具有以下特点:

(1)逻辑资源丰富,逻辑单元(LE)数量为2910个。

(2)有104个可用I/O引脚,I/O输出可以根据需要调整驱动能力,并具有压摆率控制、三态缓冲、总线保持等功能:整个器件的I/0引脚分为四个区,每个区可以独立采用不同的输入电压,并可提供不同电压等级的I/0输出。

(3)多电压接口,支持LVTTL,LVCMOS,LVDS等I/0标准。

(4)灵活的时钟管理,片内配有一个锁相环(PLL)电路,可以提供输入时钟的1~32倍频或分频、156~417ps相移和可变占空比的时钟输出,输出时钟的特性可直接在开发软件Quartos II里设定。经锁相环输出的时钟信号既可以作为内部的全局时钟,也可以输出到片外供其它电路使用。

(5)内有SignalTap嵌入式逻辑分析器,极大地方便了设计者对芯片内部逻辑进行检查,而不需要将内部信号输出到I/O管脚上。

3.设计电路模块及原理

3.1下载线电路

Altera器件的编程连接硬件包括:ByteBlaster并口下载电缆、ByteBlasterMV并口下载电缆、MasterBlaster串口/USB通信电缆、BitBlaster串口下载电缆。 本设计采用了ByteBlasterMV串口口下载电缆。

ByteBlasterMV串口下载电缆采用两种下载模式:被动串行模式和JTAG仿真下载模式。

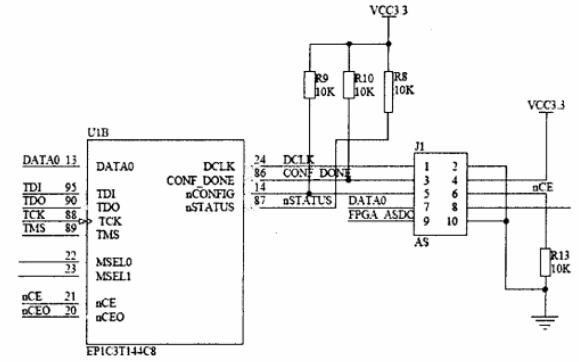

①被动串行模式(PS)

图2 PS下载接口电路

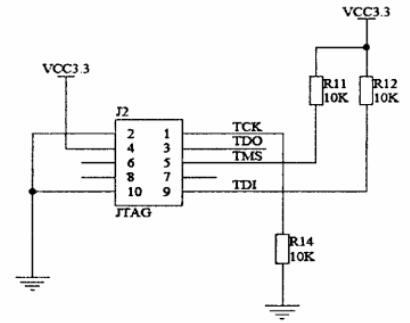

②JTAG下载模式

图3 JTAG下载接口电路

为了利用ByteBlasterMV并口下载电缆配置1.5VCyclone系列EP1C3T144,3.3V电源中应该连接上拉电阻,电缆的VCC脚连接到3.3V电源,而器件的VCCINT引脚连到相应的1.5V电源。对于PS配置,器件的VCCIO引脚必须连到2.5V或3.3V电源。对于JTAG在线配置和在线编程,电缆的VCC引脚必须连接3.3V电源。

ByteBlasterMV并口下载电缆与PC机相连的是25针插头,与PCB电路板相连的是10针插座。数据从PC机并口通过ByteBlasterMV并口电缆下载到电路板。

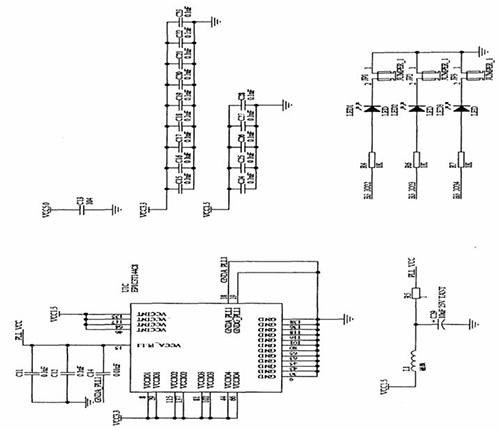

3.2电源电路

采用LM1086系列芯片为电路提供稳定的电源。LM1086是一系列工作在1.5A负载电流下,最大输出电流为1.5A的低输出电压控制器。在本设计中用于为FPGA提供1.5V和3.3V电源电压。该芯片的主要特点:

(1) 可以得到2.85V、3.3V、5.0V电压并且有不同的版本。

(2)电流限制和热保护。

(3)1.5A输出电流。

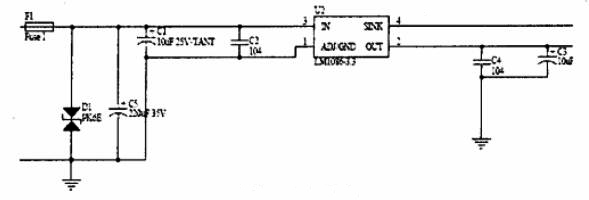

该电路将5.0V的电源电压从左端输入转化为3.3V从电路右端输出,采用的芯片是LMl086IS一3.3,为电路中需要3.3V电源电压的部分提供电压。其中F1为保险丝,可以保护电路。D1是稳压管,使电源电压更加稳定。电路中电容均为滤波之用,C2、C4为高频滤波电容,Cl、C3、C5为低频滤波电容。

图4 电源电路

将3.3V的电源电压从左端输入转化为1.5V从电路右端输出,采用的芯片是LMl086IS—ADJ,该电路同上边的电源部分原理基本相同该芯片输出电压可调,为电路中需要1.5V电源电压的部分提供电压。该电路同上边的屯源部分原理基本相同

电路的这两部分采用了LMl086系列芯片,电路中接有滤波电容,使整个电路设计非常合理输出非常稳定,可以分别担负起为电路提供稳定的3.3V、1.5V电压的的作用,保障了电路的正常工作。

3.3电源监控及复位电路

本设计的复位电路采用的芯片是IMP811。IMP811是低电压电源监控器,它的作用是用来监控供给微处理器、微控制器和其他一些数字系统的3.0V、3.3V、5.OV电源电压。在本电路中用于监控FPGA的3.3V电源电压,并且是复位电路的重要组成部分。它的主要特点有:

(1)6μA输出电流。

(2)可监视3.OV、3.3V、5.0V电源电压。

(3)手工复位输入。

(4)电压低于1.1V复位有效。

根据对于该芯片的介绍可知电路的工作原理如下:

当输入的电源电压VCC3.3不稳定即超出了IMP811允许的范围时,芯片会自动由nReset输出复位信号对电路进行保护,防止电路的元器件被烧坏另外,此电路还有手动复位键RESETl,可由IMP81l的nMR输入,为电路提供手动复位信号,用于在电路不能正常工作时,将整个电路重新启动。

3.4其他电路设计

①本设计的各个电源都接有0.1μ退偶电容,这些电容在做板时必须摆在各个芯片周围用来滤除电源中的高频杂波,保证电路中各个芯片正常工作。

②本设计选用的晶振为50MHZ,它可以为整个电路提供时钟信号。

③本设计的FPGA中配有一个锁相环,由1.5V电源经过滤波电路为其提供工作电压。

4.开发板整体设计图

开发板原理图

开发板电路图

结语

以上就是基于EP1C3T144C8的开发板设计的介绍了。本文结合FPGA结构原理和元件特性及EDA设计技术,对开发板的设计进行了研究。由电路的结构原理可以看出,本设计只做了外围电路的接口,没有完成与之配套的外围电路设计。为此,可以进一步设计更多的外围扩展电路来实现不同的扩展功能。

电话:18923864027(同微信)

QQ:709211280

〈烜芯微/XXW〉专业制造二极管,三极管,MOS管,桥堆等,20年,工厂直销省20%,上万家电路电器生产企业选用,专业的工程师帮您稳定好每一批产品,如果您有遇到什么需要帮助解决的,可以直接联系下方的联系号码或加QQ/微信,由我们的销售经理给您精准的报价以及产品介绍