CPLD (Complex Programmable Logic Device)直译的话称为复杂可编程逻辑芯片,是从PAL和GAL器件发展出来的器件,相对而言规模大,结构复杂,属于大规模集成电路范围。适合控制密集型数字型数字系统设计,其时延控制方便。CPLD是目前集成电路中发展最快的器件之一。

1.特点

CPLD具有编程灵活、集成度高、设计开发周期短、适用范围宽、开发工具先进、设计制造成本低、对设计者的硬件经验要求低、标准产品无需测试、保密性强、价格大众化等特点,可实现较大规模的电路设计,因此被广泛应用于产品的原型设计和产品生产(一般在10,000件以下)之中。几乎所有应用中小规模通用数字集成电路的场合均可应用CPLD器件。CPLD器件已成为电子产品不可缺少的组成部分,它的设计和应用成为电子工程师必备的一种技能。

CPLD

2.组成

复杂的可编程逻辑器件CPLD规模大,结构复杂,属于大规模集成电路范围。

CPLD有五个主要部分:逻辑阵列块、宏单元、扩展乘积项、可编程连线阵列和I/O控制块。

2.1逻辑阵列块(LAB)

一个逻辑阵列块由16个宏单元的阵列组成,多个LAB通过可编程阵列(PIA)和全局总线连接在一起。全局总线从所有的专用输入、I/O引脚和宏单元馈入信号。对于每个LAB有下列输入信号。

来自作为通用逻辑输入的PIA的36个信号

全局控制信号,用于寄存器辅助功能

从I/O引脚到寄存器的直接输入通道

2.2宏单元

MAX7000系列中的宏单元由3个功能块组成:逻辑阵列、乘积项选择矩阵和可编程寄存器。各部分可以被独自配置为时序逻辑和组合逻辑工作方式。其中逻辑阵列实现组合逻辑,可以为每个宏单元提供5个乘积项。乘积项选择矩阵分配这些乘积项作为到“或门”和“异或门”的主要逻辑输入,以实现组合逻辑函数,或者把这些乘积项作为宏单元中寄存器的辅助输入:如清零、置位、时钟和时钟使能控制。

每个宏单元中的触发器可以单独地编程为具有可编程时钟控制的D、T、JK或RS触发器的工作方式。触发器的时钟、清零输入可以通过编程选择使用专用的全局清零和全局时钟,或使用内部逻辑(乘积项逻辑阵列)产生的时钟和清零。触发器也支持异步清零和异步置位功能,乘积项选择矩阵分配乘积项来控制这些操作。如果不需要触发器,也可以将此触发器旁路,信号直接输给PIA或输出到I/O引脚,以实现组合逻辑工作方式。

2.3扩展乘积项

每个宏单元的一个乘积项可以反相回送到逻辑阵列。这个“可共享”的乘积项能够连到同一个LAB中的任何其它乘积项上。尽管大多数逻辑函数能够用每个宏单元中的5个乘积项实现,但在某些复杂的逻辑函数中需要附加乘积项。为提供所需的逻辑资源,可以利用另一个宏单元,MAX70000结构也允许利用共享和并联扩展乘积项,这两种扩展项可作为附加的乘积项直接送到本LAB的任意宏单元中。利用扩展项可保证在实现逻辑综合时,用尽可能少的逻辑资源实现尽可能快的工作速度。

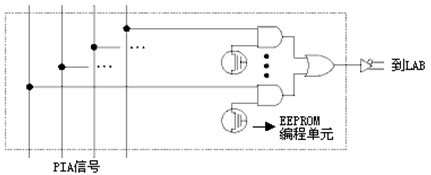

2.4可编程连线阵列PIA

通过可编程连线阵列可将各LAB相互连接构成所需的逻辑。这个全局总线是可编程的通道,它能把器件中任何信号源连到其目的地。所有MAX7000系列器件的专用输入、I/O引脚和宏单元输出均馈送到PIA,PIA可把这些信号送到整个器件内的各个地方。只有每个LAB所需的信号才真正给它布置从PIA到该LAB的连线,如图是PIA信号布线到LAB的方式。

PIA信号布线到LAB的方式

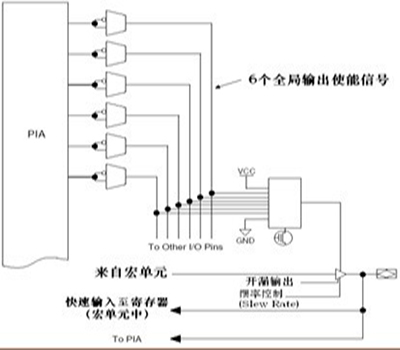

2.5I/O控制块

I/O控制块允许每个I/O引脚单独地配置成输入/输出和双向工作方式。所有I/O引脚都有一个三态缓冲器,它能由全局输出使能信号中的一个控制,或者把使能端直接连接到地(GND)或电源(VCC)上。MAX7000系列器件的I/O控制框图如图所示。MAX7000器件有6个全局输出使能信号,它们可以由以下信号驱动:两个输出使能信号、一个I/O引脚的集合、一个I/O宏单元的集合,或者是它“反相”后的信号。

I O控制框图

当三态缓冲器的控制端接地(GND)时,其输出为高阻态,而且I/O引脚可作为专用输入引脚。当三态缓冲器的控制端接电源(VCC)时,输出使能有效。

MAX7000结构提供了双I/O反馈,且宏单元和引脚的反馈是相互独立的。当I/O引脚配置成输入时,有关的宏单元可以用于隐含逻辑。

3.优势

(1)用CPLD来开发数字电路,可以大大缩短设计时间,减少PCB面积,提高系统的可靠性。

(2)CPLD还可以做数字IC设计的前端验证,用这种方式可以很大程度上降低IC设计的成本。

(3)CPLD能完成任何数字器件的功能,上至高性能CPU,下至简单的74电路,都可以用FPGA/CPLD来实现。

(4)CPLD如同一张白纸或是一堆积木,工程师可以通过传统的原理图输入法,或是硬件描述语言自由的设计一个数字系统。通过软件仿真,我们可以事先验证设计的正确性。在PCB完成以后,还可以利用CPLD的在线修改能力,随时修改设计而不必改动硬件电路。

4.使用方法

CPLD是一种用户根据各自需要而自行构造逻辑功能的数字集成电路。其基本设计方法是借助集成开发软件平台,用原理图、硬件描述语言等方法,生成相应的目标文件,通过下载电缆(“在系统”编程)将代码传送到目标芯片中,实现设计的数字系统。这里以抢答器为例讲一下它的设计(装修)过程,即芯片的设计流程。

CPLD的工作大部分是在电脑上完成的。打开集成开发软件(Altera公司 Max+pluxII)→画原理图、写硬件描述语言(VHDL,Verilog)→编译→给出逻辑电路的输入激励信号,进行仿真,查看逻辑输出结果是否正确→进行管脚输入、输出锁定(7128的64个输入、输出管脚可根据需要设定)→生成代码→通过下载电缆将代码传送并存储在CPLD芯片中。7128这块芯片各管脚已引出,将数码管、抢答开关、指示灯、蜂鸣器通过导线分别接到芯片板上,通电测试,当抢答开关按下,对应位的指示灯应当亮,答对以后,裁判给加分后,看此时数码显示加分结果是否正确,如发现有问题,可重新修改原理图或硬件描述语言,完善设计。设计好后,如批量生产,可直接复制其他CPLD芯片,即写入代码即可。如果要对芯片进行其它设计,比如进行交通灯设计,要重新画原理图、或写硬件描述语言,重复以上工作过程,完成设计。这种修改设计相当于将房屋进行了重新装修,这种装修对CPLD来说可进行上万次。

电话:18923864027(同微信)

QQ:709211280

〈烜芯微/XXW〉专业制造二极管,三极管,MOS管,桥堆等,20年,工厂直销省20%,上万家电路电器生产企业选用,专业的工程师帮您稳定好每一批产品,如果您有遇到什么需要帮助解决的,可以直接联系下方的联系号码或加QQ/微信,由我们的销售经理给您精准的报价以及产品介绍