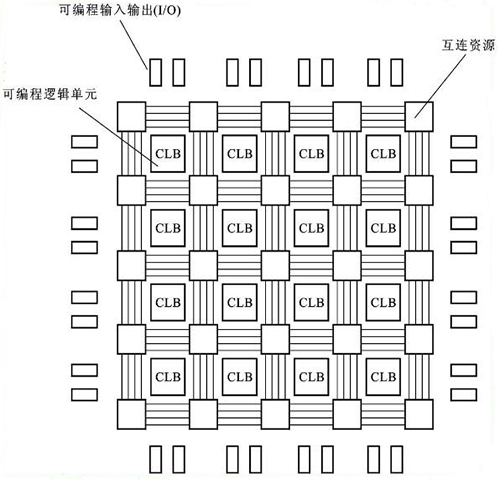

FPGA 器件属于专用集成电路中的一种半定制电路,是可编程的逻辑列阵,能够有效的解决原有的器件门电路数较少的问题。FPGA的基本结构包括可编程输入/输出单元,可配置逻辑块,数字时钟管理模块,嵌入式块RAM,布线资源,内嵌专用硬核,底层内嵌功能单元。每个单元简介如下:

FPGA基本结构

1.可编程输入/输出单元(I/O单元)

目前大多数FPGA的I/O单元被设计为可编程模式,即通过软件的灵活配置,可适应不同的电器标准与I/O物理特性;可以调整匹配阻抗特性,上下拉电阻;可以调整输出驱动电流的大小等。

2.可编程逻辑单元

FPGA的基本可编程逻辑单元是由查找表(LUT)和寄存器(Register)组成的,查找表完成纯组合逻辑功能。FPGA内部寄存器可配置为带同步/异步复位和置位、时钟使能的触发器,也可以配置成为锁存器。FPGA一般依赖寄存器完成同步时序逻辑设计。

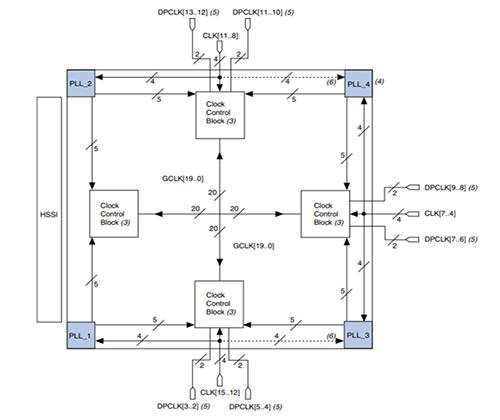

3.时钟管理

时钟资源部分主要包括全局时钟树和锁相环两部分。

全局时钟树又称全局时钟网络,负责把时钟分配到器件内部的各个单元,控制器件内部所有资源。锁相环则可以完成分频、倍频、移项等相关时钟的基本操作。全局时钟树是一种时钟网络结构,可以为FPGA内部的所有资源提供时钟信号,这些资源包括内部的寄存器、内部的存储器、输入输出管脚寄存器等。

锁相环在FPGA中除了分频、倍频操作外,还进场用于内部时钟和外部时钟保持沿同步,提供需要的外部时钟输出等。

全局时钟树

4.嵌入式块RAM

目前大多数FPGA都有内嵌的块RAM。嵌入式块RAM可以配置为单端口RAM、双端口RAM、伪双端口RAM、CAM、FIFO等存储结构。

CAM,即为内容地址存储器。写入CAM的数据会和其内部存储的每一个数据进行比较,并返回与端口数据相同的所有内部数据的地址。简单的说,RAM是一种写地址,读数据的存储单元;CAM与RAM恰恰相反。

除了块RAM,Xilinx和Lattice的FPGA还可以灵活地将LUT配置成RAM、ROM、FIFO等存储结构。

5.布线资源

布线资源连通FPGA内部所有单元,连线的长度和工艺决定着信号在连线上的驱动能力和传输速度。布线资源的划分:

(1)全局性的专用布线资源:以完成器件内部的全局时钟和全局复位/置位的布线;

(2)长线资源:用以完成器件Bank间的一些高速信号和一些第二全局时钟信号的布线。

(3)短线资源:用来完成基本逻辑单元间的逻辑互连与布线;

(4)其他:在逻辑单元内部还有着各种布线资源和专用时钟、复位等控制信号线。

由于在设计过程中,往往由布局布线器自动根据输入的逻辑网表的拓扑结构和约束条件选择可用的布线资源连通所用的底层单元模块,所以常常忽略布线资源。其实布线资源的优化与使用和实现结果有直接关系。

6.底层嵌入功能单元

底层嵌入功能模块主要指DLL(Delay Locked Loop)、PLL(Phase Locked Loop)、DSP和CPU等软处理核(Soft Core)。

7.内嵌专用硬核

内嵌专用硬核是相对底层嵌入的软核而言的,指FPGA处理能力强大的硬核(Hard Core),等效于ASIC电路。为了提高FPGA性能,芯片生产商在芯片内部集成了一些专用的硬核。

以上就是FPGA的基本结构介绍了。由于FPGA具有布线资源丰富,可重复编程和集成度高,投资较低的特点,在数字电路设计领域得到了广泛的应用。

电话:18923864027(同微信)

QQ:709211280

〈烜芯微/XXW〉专业制造二极管,三极管,MOS管,桥堆等,20年,工厂直销省20%,上万家电路电器生产企业选用,专业的工程师帮您稳定好每一批产品,如果您有遇到什么需要帮助解决的,可以直接联系下方的联系号码或加QQ/微信,由我们的销售经理给您精准的报价以及产品介绍