随着数字技术的飞速发展,高精度大动态范围数字/模拟(D/A)转换器的出现和广泛应用,用数字控制方法从一个标准参考频率源产生多个频率信号的技术,即直接数字合成(DDS)技术异军突起;其具有分辨率高、频率变换快、相位噪声低,信号纯度高等优点,因此,在雷达及通信等领域有着广泛的应用前景。文中介绍了一种高性能DDS芯片AD9850的基本原理和工作特点,阐述了如何利用此芯片设计一种频率在0~50kHz内变化、相位正交的信号源,给出了AD9850芯片和MCS51单片机的硬件接口和软件流程。

1.AD9850芯片介绍

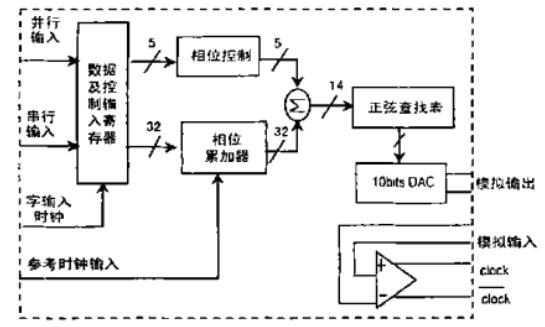

AD9850是AD 公司生产的最高时钟为125MHz、采用先进的CMOS技术的直接频率合成器,主要由可编程DDS系统、高性能模数变换器(DAC)和高速比较器3部分构成,能实现全数字编程控制的频率合成,并具有时钟产生功能,其原理框图如图1所示。

图1 AD9850原理框图

AD9850的DDS系统包括相位累加器和正弦查找表,其中相位累加器由一个加法器和一个32位相位寄存器组成,相位寄存器的输出与外部相位控制字(5位)相加后作为正弦查找表的地址。正弦查找表实际上是一个相位/幅度转换表,它包含一个正弦波周期的数字幅度信息,每一个地址对应正弦波中0~3608范围的一个相位点。查找表把输入地址的相位信息映射成正弦波幅度信号,然后驱动10 bit的DA变换器,输出2个互补的电流,其幅度可通过外接电阻进行调节。AD9850还包括一个高速比较器,将DA变换器的输出经外部低通滤波器后接到此比较器上即可产生一个抖动很小的方波,这使得AD9850可以方便地用作时钟发生器。

AD9850包含40位频率/相位控制字,可通过并行或串行方式送入器件:并行方式指连续输入5次,每次同时输入8位(1个字节);串行方式则是在一个管脚完成40位串行数据流的输入。这40位控制字中有32位用于频率控制,5位用于相位控制,1位用于掉电( power down)控制,2位用于选择工作方式。

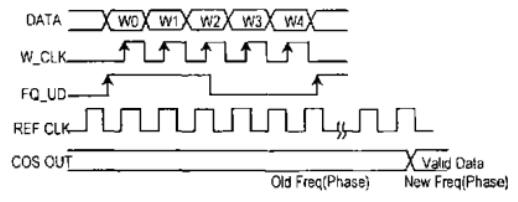

在并行输入方式下,通过8位总线DO~D7将外部控制字输入到寄存器,在 W_ CLK(字输入时钟)的上升沿装入第一个字节,并把指针指向下一个输入寄存器,连续5个W- CLK 的上升沿读入5个字节数据到输入寄存器后,W- CLK的边沿就不再起作用。然后在FQ-UD(频率更新时钟)上升沿到来时将这40位数据从输入寄存器装入到频率/相位寄存器,这时DDS输出频率和相位更新一次,同时把地址指针复位到第一个输入寄存器以等待下一次的频率/相位控制字输入。图2即为AD9850控制字并行输入时序。

图2 控制字并行输入时序

2.硬件设计

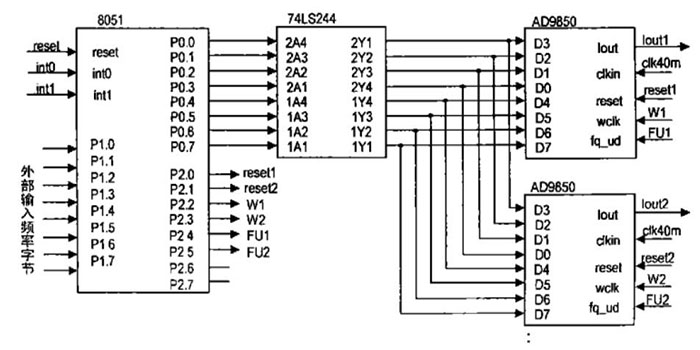

要产生两路相位正交、频率可由外部控制的正弦信号,必须通过单片机编程来完成外部输入的频率数据(3个字节)与DDS芯片(AD9850)内部频率相位控制字(5个字节)间的转换。单片机 8051与AD9850芯片的接口既可采用并行方式,也可采用串行方式,本设计采用的是8位并行接口方式。

由于需要产生I/Q两路正弦信号,因此使用了2片AD9850芯片,这两路的频率相同,相位差90°。单片机8051的P1口( P1.0~P1.7脚)用作外部空市字输入,通过中断1和中断0读入外部频率数据,连续读3次,对应频率值的二进制数;单片机的P0口( P0.0~ P0.7脚)用作频率/相位控制字输出,通过8位缓冲器74LS244作数据缓冲后加到2片AD9850芯片的8位控制字输入端(D0~D7脚),同时产生相应的DDS时序控制信号(一路复位reset l、二路复位reset2、一路字输入时钟W1、二路字输入时钟W2、一路频率更新时钟FU 1、二路频率更新时钟FU2) 加到AD9850芯片的对应管脚。AD9850的外部参考时钟信号( clk40m)频率为40 MHz,由晶体振荡器产生。单片机8051的复位信号(reset )、中断0和中断1控制信号( int0、int 1)由外部控制系统给出,从而实现例路相位正交、频率可控的正弦信号。该DDS信号源的硬件接口电路如图3所示。

图3 DDS信号源硬件接口电路图

3.软件控制

此程序的功能就是要将外部输入的频率数据按照一定协议和算法变换成DDS芯片(AD9850)所能接受的格式,并送出相应的频率相位控制信号,从而使AD9850能产生两路相位正交、频率可控的正弦信号。下面给出程序设计输入、输出、变换算法及流程图。

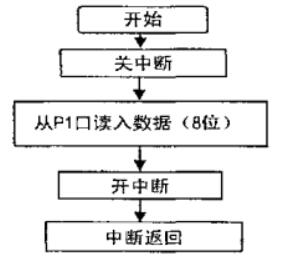

3.1输入

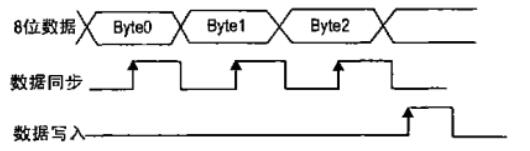

数据同步:上升沿时读入1个字节的频率数据,作为int1中断输入:

数据写入:上升沿时频率更新1次,作为int0中断输入;

8位数据:输入的频率字节。分3次输入,如图4所示。

图4 信号源控制程序输入

3.2输出

单片机控制程序将产生下述输出信号加到DDS芯片(AD9850)的对应脚:

resetl:一路DDS复位(一路AD9850第22脚);

reset2:二路DDS复位(二路AD9850第22脚);

w 1:一路数据同步(一路AD9850第7脚);

w2:二路数据同步(二路AD9850第7脚);

ful:一路数据写入(一路 AD9850第8脚);

fu2:二路数据写入(二路AD9850第8脚);

PO 口(P0.0~P0.7):8位频率/相位数据输出( AD9850的D0~ D7脚)。

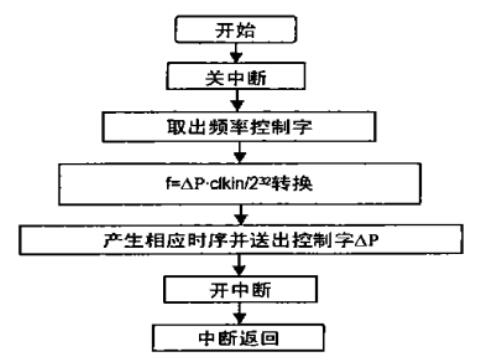

3.3算法

程序中单片机输入频率数据F(3个字节)与输出频率数据∆P( 4个字节)间的变换算法见下式:

其中CIKN为外部参考时钟( 40 000 000 Hz)。

3.4程序流程

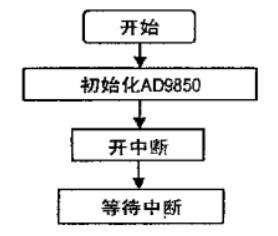

整个程序由主程序、中断0子程序、中断1子程序三部分构成。主程序流程如图5所示,中断1子程序流程如图6所示,中断0子程序流程如图7所示。

图5 主程序流程图

图6 中断1子程序流程图

图7 中断0子程序流程图

小结

以上就是基于DDS芯片AD9850的信号源设计介绍了。通过对设计的DDS信号源在不同频率下的输出波形进行了测试,结果完全能达到所要求的性能指标。目前广泛应用于电子测量、跳频通信、雷达系统等领域。

电话:18923864027(同微信)

QQ:709211280

〈烜芯微/XXW〉专业制造二极管,三极管,MOS管,桥堆等,20年,工厂直销省20%,上万家电路电器生产企业选用,专业的工程师帮您稳定好每一批产品,如果您有遇到什么需要帮助解决的,可以直接联系下方的联系号码或加QQ/微信,由我们的销售经理给您精准的报价以及产品介绍