晶振是各整机电子设备的核心部件,它在一定程度上决定着整机的性能指标。晶振的相位噪声指标是影响信号源的关键因素之一,对整机设备的性能参数有着重要意义,也是晶振非常关键的指标。本文介绍了一种小型超低相噪恒温晶振的设计,重点阐述了有载品质因数(Q)值、电路结构等对相噪的影响,并基于改进型的巴特勒振荡电路在小体积下进行了超低相噪恒温晶振的设计,对其主振电路、放大电路、稳压电路等进行了概要的分析。

1.理论分析

在晶体振荡电路中,三极管、二极管和电阻、电容、电感等元件都存在噪声,其中以产生振荡信号的三极管噪声影响最大;而电感、电容等元件,在噪声分析中,可近似为无噪声元件口。在放大器上加正反馈元件构成振荡器时,噪声将对振荡器信号进行调制而形成白噪声调相、白噪声调频和闪变噪声调相、闪变噪声调频等噪声模式。

根据LESSON模型分析,晶体振荡器的相位噪声与晶体振荡电路的有载品质因数(Q)值密切相关,有载Q值越高,相位噪声恶化的程度越低。因此在低相噪晶振设计中,通常围绕如何提高有载Q值开展研究。晶体振荡电路的有载Q值主要由振荡电路中晶体谐振器自身Q值以及所采用的振荡电路拓扑结构所决定。晶体谐振器自身的Q值受限于晶体制作工艺,不可能无限制提升,因此如何进一步提升晶体谐振器在振荡电路中的有载Q值是低相噪晶振设计的关键。

常用的晶体振荡电路主要有并联反馈型振荡电路和串联反馈型振荡电路。并联振荡电路中,晶体谐振器工作在串、并联谐振频率之问,晶体呈感性;常用的并联振荡电路包括皮尔斯电路和考毕兹电路。串联振荡电路是将晶体串联在正反馈电路中,晶体谐振器工作在串联谐振频率,晶体呈纯阻性。常用的串联振荡电路通常为巴特勒电路。

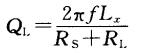

要提高晶体谐振器在电路的有载Q值,必须选取有载Q值匹配相对较好的振荡电路形式。晶体的有载Q值为:

式中:L为晶体等效电感;R为晶体等效电阻;R为晶体负载电阻。

由于电路中的电阻损耗,电路中晶体谐振器有载Q值通常比晶体谐振器自身绝对Q值小。为使Q值损耗最小,应尽量使晶体的R最小,以便整个电路的Q值不会因负载电阻而显著恶化。在皮尔斯电路和考毕兹电路等并联振荡电路中,晶体分别接在三极管的集电极和基极,等效负载相对较大;而在巴特勒串联振荡电路中,晶体谐振器串接在发射极来提供高频负反馈,等效负载电阻小,有载Q值相对于前两种电路有一定优势。同时,采用并联振荡电路还需要加入晶体谐振器的B模抑制网络,会进一步降低晶体谐振器Q值。因此,理论上高频振荡器采用串联振荡电路能达到比并联振荡电路更低的噪声,在电路中具有良好的有载Q值。

2.仿真分析

电路拓扑结构确定后,在参数设计上,需进行充分的仿真验证。对晶体振荡器设计的仿真,重点要解决晶体谐振器和晶体管的建模问题,其次就是对振荡电路结构的选择,从而对晶体振荡器的设计进行仿真分析,并对电路参数进行优化。

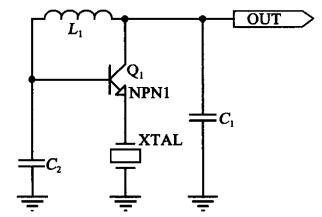

依据理论分析,为保证低相位噪声水平,振荡电路选择了有载Q值良好的巴特勒串联振荡电路。在巴特勒电路中晶体串接在主振放大器的发射极,它提供高频负反馈,而接在电路输出端的电容分压器提供正反馈。晶体谐振器在振荡电路中工作在自身的串联谐振频率上,起到对谐振频率进行高(选频的作用)。巴特勒振荡电路的交流等效图如图1所示。

图1 等效电路图

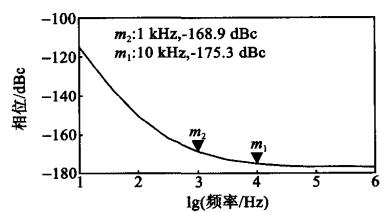

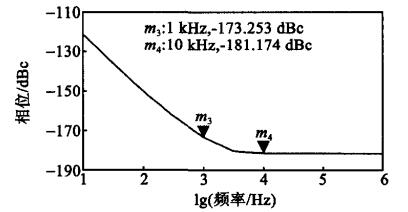

采用仿真手段,对上述振荡电路进行仿真分析。图2为采用谐波平衡仿真分析得到的相噪仿真结果。

图2 相位噪声仿真结果

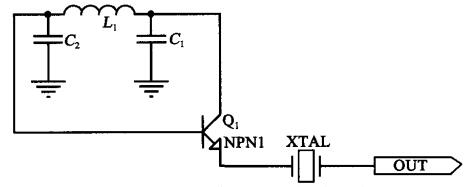

结合工程设计经验,我们对巴特勒电路结构进行改进,将振荡信号直接从石英谐振器引出,这样可以充分利用晶体谐振器的高Q值选频特性。改进后的巴特勒振荡电路交流等效图如图3所示。

图3 改进型等效电路图

采用仿真工具,对改进型的巴特勒电路进行了分析,通过参数优化,得到的相噪仿真结果如图4所示。

图4 改进型相噪仿真结果

由图4可看出,采用该改进型巴特勒结构的振荡电路,相位噪声有明显改进。在产品实际设计中,会受到部分不确定附加噪声的影响,相噪结果会与仿真分析存在偏差,但仿真分析仍然为产品的实际研制起到了一定的指导作用。

3.产品研制

3.1器件选型

在低相噪晶振设计中,器件选型是关系设计成败的关键因素之一,特别是对晶体谐振器、三极管等关键器件的选择。

在晶体谐振器的选择上,对于切型、Q值、泛音次数、频差、零温度系数点(即拐点)、静态电容、等效电阻等参数都要进行慎重考虑和正确选取,特别是在本文低相噪设计中,为保证电路中的高有载Q值,对晶体谐振器Q值的选择尤其重要Es3。通过综合考虑,本文选用了具有更高Q值和稳定性的SC切5次泛音高Q晶体谐振器。

在三极管的选择上,本文重点考虑了噪声系数,并兼顾高增益、低温漂、小封装等要求,噪声系数<1最为理想。

在其他器件的选择上,在满足封装要求的前提下,均重点考虑低噪声的要求。

3.2电路设计

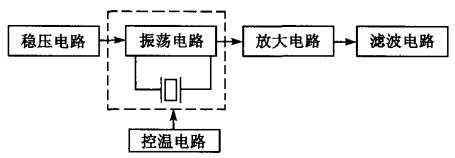

本设计中电路组成框图如图5所示。

图5 晶振电路组成框图

(1)振荡电路

传统的巴特勒结构电路将晶体谐振器连接在反馈回路中,振荡模式较复杂,调试困难。本文对传统巴特勒电路进行改进(见图3),将振荡信号直接从晶体谐振器引出,通过合理的电路及参数设计,可使输出信号具有极低的相位噪声。

(2)稳压电路

晶体振荡器对电源线上的噪声尤其敏感,特别当晶振调谐范围较宽时,因此低噪声晶振振荡电路的稳压电路设计极其重要。在本设计中,我们选用低噪声与纹波的线性稳压器件,并连接到一个具有大的电源纹波抑制作用而同时具有低噪声特性的运算放大器来作为供电单元。在电路板布局时,对电源滤波做充分考虑,使电源纹波对各级电路的影响达到最小。同时在变容二极管调谐端加入低噪声运算放大器进行隔离,以有效降低调谐端噪声电压对晶振相位噪声带来的影响。

(3)放大电路

本设计中振荡信号直接从晶体谐振器引出,因此选用具有更低输入阻抗的共基极低噪声放大器作为晶振的放大级,以便能与晶体谐振器更好地实现阻抗匹配,提高有载Q值。三极管选用低噪声晶体管,其偏置电路使用与主振电路相同的低噪声偏置,但放大器的直流工作点与主振电路不同,充分保证放大电路工作在线性状态。同时在放大电路中加入适当的负反馈,降低闪烁调相(1/f)和闪烁调频(1/f³)噪声。

(4)滤波电路

本设计在输出端加入了带通滤波电路,使振荡电路与输出端有效隔离,减小负载变化对主振状态的影响,同时提高输出信号的频谱纯度。

(5)控温电路

为保证晶振的短期稳定度及近端相噪,需采用精密控温的方式来降低外界环境变化对晶振振荡频率的影响。本设计选择了比例积分反馈的连续式控温电路,通过PID比例积分反馈回路对温度进行精确控制,提高控温电路的灵敏度、控温精度及环境适应性。

3.3测试结果

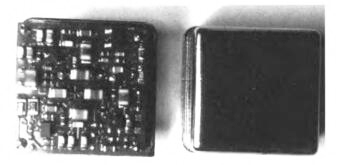

本文设计的100MHz小型超低相噪恒温晶体振荡器实物照片如图6所示。

图6 晶振实物照片

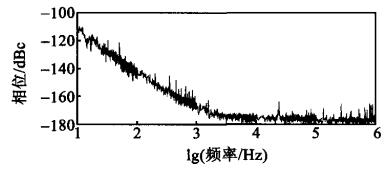

相位噪声实际测试曲线如图7所示。由图可见,本文研制的100MHz小型超低相噪恒温晶振体积达到20mm×20mm×10mm,相噪指标最优达到一168dBc/Hz@1kHz,达到了预期的研制目标。

图7 相位噪声测试曲线

结束语

本文总结了小型超低相噪恒温晶振的设计方案。该文研制的100MHz小型超低相噪恒温晶振体积达到20mm×20ram)<10mm,相噪指标最优达到一168dBc/Hz@1kHz,达到了预期的研制目标。其具备良好的相位噪声性能及小封装尺寸,可满足新一代电子装备对晶振体积和相噪指标的严苛要求,具备很好的应用前景。

电话:18923864027(同微信)

QQ:709211280

〈烜芯微/XXW〉专业制造二极管,三极管,MOS管,桥堆等,20年,工厂直销省20%,上万家电路电器生产企业选用,专业的工程师帮您稳定好每一批产品,如果您有遇到什么需要帮助解决的,可以直接联系下方的联系号码或加QQ/微信,由我们的销售经理给您精准的报价以及产品介绍