电容去耦是电源完整性(Power Integrity,PI)设计里面很重要的一部分,而PI设计则是为了保证电源分配网络(Power Distribution Network,PDN)系统能够满足负载芯片对电源的要求。

PDN主要作用:1、为负载提供干净的供电电压;2、为信号提供低噪参考路径。

电源噪声

电源噪声有啥影响,打个极端的比方,IC的高电平判决门限是1.2V,我的电源噪声是1.3V,当我噪声传递到了这个IC的时候,噪声会造成误判决。大部分时候没有这么严重,但是噪声会影响系统的可靠性和稳定性。

而对于噪声抑制,在设计的时候,并不是等着噪声出现了之后再去想办法消除或者是减轻它,做硬件的同学们应该知道,问题出现后再去解决,这样代价是非常大的。一般都是在设计之初就把各种预防措施都考虑进去,尽可能的规避掉可能会发生的问题,不要幻想着可以试错(这可就是改板了,那都是经费呀)。

电源噪声的来源:

1、硬件本身引入的,比如说稳压电源的纹波,当前稳压电源分为线性电源和开关电源,线性电源的纹波较小,开关电源的纹波较大,对于电源噪声敏感的电路一般不建议使用开关电源(不过随着技术的提升感觉现在开关电源纹波也能做的很小了);

2、电源无法实时的响应负载电流需求,一般电源依据负载的功耗需求需要实时的对输出电流进行调整,否则当负载功耗增大的时候,会导致电源输出电压被拉低。但是对于电源本身,是有一个调整响应时间的,一般是us级,所以,当负载电流瞬态变化频率超过这一范围的时候,稳压电源无法及时响应,就会造成链路上电压出现跌落,这也是电源噪声的一种;

3、板上压降,有路径的地方就有阻抗,有负载就会有电流,有电流有阻抗就会有压降。加上PCB上的各种寄生参数,寄生电感和寄生电容对频率敏感,而负载功耗一般也是动态变化的,具有交流特性,两者一结合就造成的负载端电压的波动,由阻抗产生的噪声,也是电源噪声的一种;

4、PCB层间噪声,PCB是有多层的,信号在传输穿过不同平面的同时会产生返回信号,信号有时候来不及通过去耦电容进行换层,就只能通过耦合的方式进行换层,对于不同的平面来说就相当于电容在进行充放电,引起局部噪声(实际上,通过去耦电容一样会有噪声,后面会讲到)。

电容去耦原理

实际电路中,我们会看到芯片周围布满了电容,这些电容称为去耦电容,为当前硬件设计中解决噪声问题的主要方式。我们可以通过下面两种方式来对电容去耦有个初步的理解。

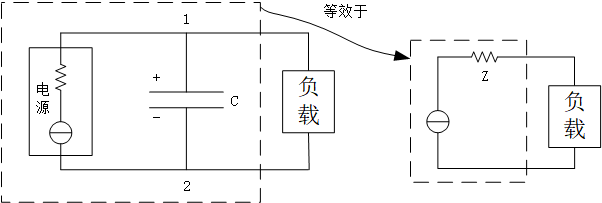

1、阻抗角度

可以通过一张图来理解:

首先,我们对PDN的要求就是不论负载端瞬态电流如何变化,都得保证负载两端电压的稳定,负载端电压的变化要尽可能的小。依据等效电路,可以得到△U=Z*△I(此时电源为理想电源,阻抗都由Z来等效了,理想电源输出的电压是恒定的,那么z与负载就会形成一个分压效果,进而影响负载两端电压的稳定)。由于瞬态电流是动态的,有交流特性,而去耦电容刚好在交流条件下表现为低阻抗(再极端点,因为电阻并联阻抗会减小,也就是电容并的越多,等效阻抗就越小),即去耦电容能够减小Z,进而减小电源噪声。

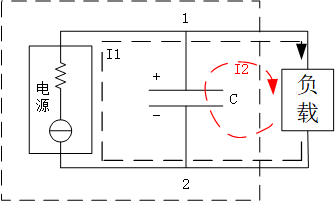

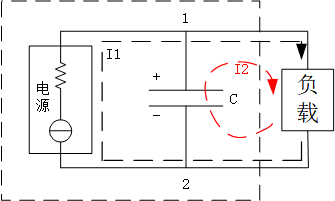

2、储能角度

同样可以通过一张图来理解:

上图可以看到,负载相当于同时由电源和电容进行供电,当负载电流稳定的时候,I2为0,负载由电源进行供电,并且电容电压等于电源供电电压,此时电容是存储满了电量的,当负载电流变化的时候,由于电源存在响应时间,无法立即响应负载电流的变化,因此负载端电压会下降,此时电容感受到负载端电压的变化,此时电容开始放电,I2不再为0,开始为负载供电,而I=C*dV/dt,当电容的C足够大的时候,只需要很小的dV就能够提供很大的电流,用以满足负载变化的需求,进而控制负载端电压变化不至于过大。

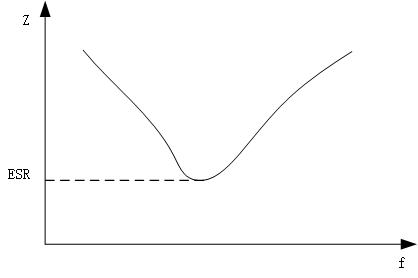

电容阻抗特性

电容简化模型如下:

ESR一般为电极,电解质的等效电阻,C为电容的容值,ESL为电极和端子的等效电感。

因此一个电容的特性阻抗Z可以表示为:

Z=ESR+j2πfESL+1/j2πfC=ESR+j(2πfESL- 1/2πfC)

当频率很低的时候,2πfESL远小于1/2πfC,电流超前于电压,电容的阻抗随频率增加而减小,电容呈现容性;当频率很高的时候,2πfESL大于1/2πfC,电流滞后于电压,电容的阻抗随频率增加而增大,电容呈现感性;2πfESL=1/2πfC,f= 1/(2π√(ESLC)),电容呈现纯电阻特性,此时电容阻抗最小,该频率点也称为电容的自谐振频率。因此,去耦电容实际上都有一定的工作频率范围,只有在这个范围内,去耦电容的去耦效果才比较好。

复阻抗概念

Z=R+jX=R+j(XL-XC)

当X>0时,XL>XC,电压超前于电流,电路呈感性;

当X<0时,XL<XC,电压滞后于电流,电路呈容性;

当X=0时,XL=XC,电压与电流同相,电路呈纯阻性。

电话:18923864027(同微信)

QQ:709211280

〈烜芯微/XXW〉专业制造二极管,三极管,MOS管,桥堆等,20年,工厂直销省20%,上万家电路电器生产企业选用,专业的工程师帮您稳定好每一批产品,如果您有遇到什么需要帮助解决的,可以直接联系下方的联系号码或加QQ/微信,由我们的销售经理给您精准的报价以及产品介绍