上拉电阻和下拉电阻有什么用?

1、提高驱动能力:

例如,用单片机输出高电平,但由于后续电路的影响,输出的高电平不高,就是达不到VCC,影响电路工作。所以要接上拉电阻。下拉电阻情况相反,让单片机引脚输出低电平,结果由于后续电路影响输出的低电平达不到GND,所以接个下拉电阻。

2、钳位

上拉就是将不确定的信号通过一个电阻钳位在高电平,电阻同时起限流作用。下拉同理,也是将不确定的信号通过一个电阻钳位在低电平

在单片机引脚电平不定的时候,让后面有一个稳定的电平:

例如上面接下拉电阻的情况下,在单片机刚上电的时候,电平是不定的,还有就是如果你连接的单片机在上电以后,单片机引脚是输入引脚而不是输出引脚,那这时候的单片机电平也是不定的,下拉电阻的作用就是如果前面的单片机引脚电平不定的话,强制让电平保持在低电平。

3、 提高输出的高电平值

例如: 当TTL电路驱动CMOS电路时,如果电路输出的高电平低于CMOS电路的最低高电平(一般为3.5V), 这时就需要在TTL 的输出端接上拉电阻,以提高输出高电平的值

此外还有以下作用:

1、提高总线的抗电磁干扰能力,管脚悬空就比较容易接受外界的电磁干扰;

2、长线传输中电阻不匹配容易引起反射波干扰,加上、下拉电阻是电阻匹配,有效的抑制反射波干扰。

3、 如果电平用OC(集电极开路,TTL)或OD(漏极开路,CMOS)输出,那么不用上拉电阻是不能工作的, 这个很容易理解,管子没有电源就不能输出高电平了。

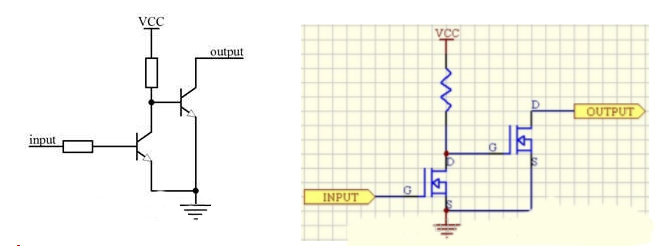

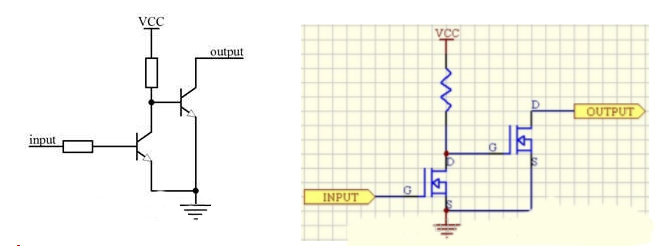

如下图所示:

集电极开路输出的结构如图1所示,右边的那个三极管集电极什么都不接,所以叫做集电极开路;和集电极开路类似,漏极开路输出;

一般情况下都需要在OUTPUT 输出口 外接上拉电阻,才能输出高电平。否则在右边三极管截止时,输出的是高阻态。

高阻态状态下便于多个三极管并联(线与逻辑) 有一个为低电平,所有的都为低电平。

上下拉使用对比:

需要注意的是,上拉电阻太大会引起输出电平的延迟。(RC延时)一般CMOS门电路输出不能给它悬空,都是接上拉电阻设定成高电平。

下拉电阻:和上拉电阻的原理差不多, 只是拉到GND去而已。 那样电平就会被拉低。 下拉电阻一般用于设定低电平或者是阻抗匹配(终端端接)。

上拉是对器件输入电流,下拉是输出电流;

上拉用来增大电流,下拉电阻是用来吸收电流。

选用原则:

上拉电阻阻值的选择原则包括:

1、从节约功耗及芯片的灌电流能力考虑应当足够大;电阻大,电流小。

2、从确保足够的驱动电流考虑应当足够小;电阻小,电流大。

3、对于高速电路,过大的上拉电阻可能边沿变平缓。

综合考虑以上三点,通常在1k到10k之间选取。对下拉电阻也有类似道理

上拉电阻偏大或偏小的影响: 400kbs

上拉电阻值过小,Vcc灌入端口的电流(Ic)将较大,这样会导致MOS管V2(三极管)不完全导通(Ib*β,有饱和状态变成放大状态,这样端口输出的低电平值增大(i2c协议规定,端口输出低电平的最高允许值为0.4v)。

如果上拉电阻过大,加上线上的总线电容,由于RC影响,会带来上升时间的增大(下降延是芯片内的晶体管,是有源驱动,速度较快;上升延是无源的外接电阻,速度慢),而且上拉电阻过大,即引起输出阻抗的增大,当输出阻抗和负载的阻抗可以比拟的时,则输出的高电平会分压而减少。

低功耗状态 上拉下拉使用注意:

带上拉或者下拉的IO口,在低功耗状态,或者配置使用的常态时,应根据IO口的状态进行相关的设置。

如果IO口没有做好处理的话,它就会在暗地里偷走功耗,而你却浑然不知。具体原因是这样的,一般的IO的内部或者外部都会有上下拉电阻,举个例子,如下图所示,假如某个IO口有个10KΩ的上拉电阻,把引脚拉到3.3V,然而当MCU进入低功耗模式的时候,此IO口被设置成输出低电平,根据欧姆定律,此引脚就会消耗3.3V/10K=0.33mA的电流,假如有四、五个这样的IO口,那么几个mA就贴进去了,太可惜了。所以在进入低功耗之前,请逐个检查IO口的状态:

如果此IO口带上拉,请设置为高电平输出或者高阻态输入;

如果此IO口带下拉,请设置为低电平输出或者高阻态输入;

总之一句话,不要把上好的电流浪费在产生热量的功能上,咱可不靠这点温度去暖手。

IO口上拉与下拉电平与IC间的连接造成的相应功耗的损失:

IO口的上下拉电阻消耗电流这一因素相对比较明显,下边咱来说一个不明显的因素:IO口与外部IC相连时的电流消耗。假如某个IO口自带上拉,而此与IO相连的IC引脚偏偏是自带下拉的,那么无论这个引脚处于什么样的电平输出,都不可避免的产生一定的电流消耗。所以凡是遇见这一类的情况,首先需要阅读外设IC的手册,确定好此引脚的的状态,做到心中有数;然后在控制MCU睡眠之前,设置好MCU的IO口的上下拉模式及输入输出状态,要保证一丝儿电流都不要被它消耗掉。

系统功耗测试。

检测出来的电流消耗很大,可实际应用消耗的功耗却不大?

是因为在测试功耗的时候MCU还连接着调试器呢!这时候大部分电流就会被调试器给掳走,平白无故的让工程师产生极度郁闷的心情。所以在测低功耗的时候,一定不要连接调试器,更不能边调试边测电流。

烜芯微专业制造二极管,三极管,MOS管,桥堆等20年,工厂直销省20%,上万家电路电器生产企业选用,专业的工程师帮您稳定好每一批产品,如果您有遇到什么需要帮助解决的,可以点击右边的工程师,或者点击销售经理给您精准的报价以及产品介绍

烜芯微专业制造二极管,三极管,MOS管,桥堆等20年,工厂直销省20%,上万家电路电器生产企业选用,专业的工程师帮您稳定好每一批产品,如果您有遇到什么需要帮助解决的,可以点击右边的工程师,或者点击销售经理给您精准的报价以及产品介绍