CD4060是由一振荡器和14位二进制串行计数器位组成,振荡器的结构可以是RC或晶振电路,CR为高电平时,计数器清零且振荡器使用无效。所有的计数器位均为主从触发器。在CP1(和CP0)的下降沿计数器以二进制进行计数。在时钟脉冲线上使用斯密特触发器对时钟上升和下降时间限制。

1.cd4060中文资料

CD4060芯片特性

1) 电压范围宽,应该可以工作在3V~15V,输入阻抗高,驱动能力差外,跟74系列的功能基本没有区别;

2) 输入时,1/2工作电压以下为0,1/2工作电压以上为1;

3) 输出时,1=工作电压;0=0V

4) 驱动能力奇差,在设计时最多只能带1个TTL负载;

5) 如果加上拉电阻的话,至少要100K电阻;

6) 唯一现在使用的可能就是计数器,CD4060的计数器可以到14级二进制串行计数

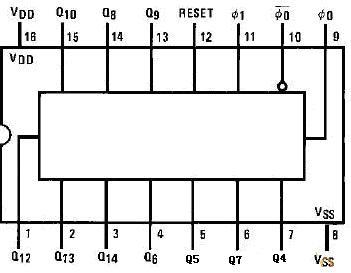

2.cd4060引脚图及功能

CD4060是14 级二进制串行计数器(分频器/振荡器)各引脚功能如下:

1、12分频输出 2、13分频输出

3 、14分频输出 4、6分频输出

5、5分频输出 6、7分频输出

7、4分频输出 8、Vss地

9、信号正向输出 10、信号反向输出

11、信号输入 12、复位信号输入

13、9分频输出 14、8分频输出

15、10分频输出 16、VDD电源

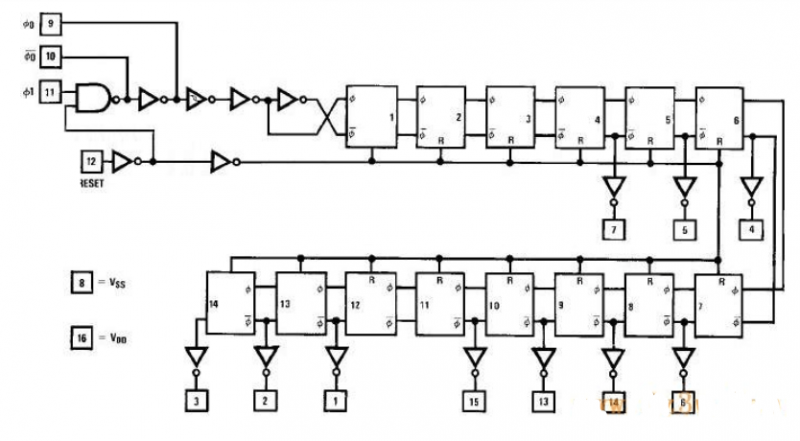

3.cd4060工作原理

CD4060构成的精确长延时原理电路工作原理:

通电后,时基振荡器震荡经过分频后向外输出时基信号。作为分频器的IC2 开始计数分频。当计数到10 时,Q4 输出高电平,该高电平经D1 反相变为低电平使VT 截止,继电器断电释放,切断被控电路工作电源。与此同时, D1 输出饿低电平经D2 反相为高电平后加至IC2 的CP 端,使输出端输出的高电平保持。电路通电使IC1、IC2 复位后,IC2 的四个输出端,均为低电平。而Q4 输出的低电平经D1 反相变为高电平,通过R4 使VT 导通,继电器通电吸和。这种工作状态为开机接通、定时断开状态。

4.cd4060内部结构

5.cd4060作用和用途

CD4060的应用电路

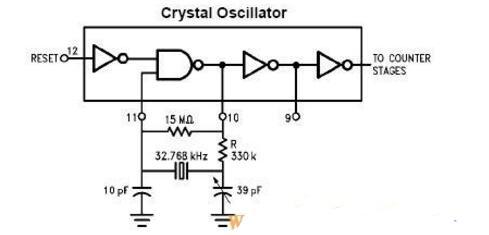

CD4060B典型振荡器连接:

上图-RC振荡器 下图-晶体振荡器

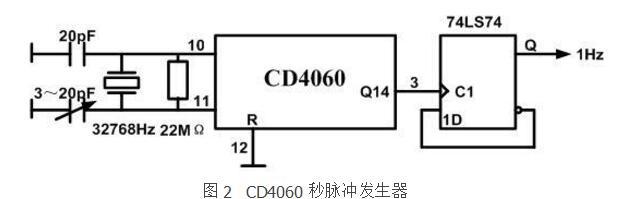

CD4060秒脉冲发生器电路:

烜芯微专业制造二极管,三极管,MOS管,桥堆等20年,工厂直销省20%,4000家电路电器生产企业选用,专业的工程师帮您稳定好每一批产品,如果您有遇到什么需要帮助解决的,可以点击右边的工程师,或者点击销售经理给您精准的报价以及产品介绍

烜芯微专业制造二极管,三极管,MOS管,桥堆等20年,工厂直销省20%,4000家电路电器生产企业选用,专业的工程师帮您稳定好每一批产品,如果您有遇到什么需要帮助解决的,可以点击右边的工程师,或者点击销售经理给您精准的报价以及产品介绍