自TTL 和 5V CMOS 成为逻辑电路的主要标准电平后,电路设计发生了较大变化。现今电子系统的复杂度不断提高,逻辑电压不断下降,使得系统内部逻辑单元的输入和输出电平不一致。比如,电路设计中常见的一种情况是 1.8V 供电的数字电路与 3.3V 供电的模拟电路之间的连接。本文主要阐述了串行数据系统中逻辑电路的工作原理及注意事项,给出了在不同逻辑电压之间转换的方法。

对逻辑电平转换的需求

越来越多的数字 IC 采用与以往不兼容的电源电压、更低的 VDD、或者 VCORE 和 VI/O 不同的双电源供电,这就提出了对于逻辑电平转换的要求。低电压混合信号 IC 如未能与其配合的数字器件的发展保持同步,也需要使用逻辑电平转换。

转换方法随着转换电平范围、需要转换的信号线数(如,一个 4 线的串行外设接口(SPI)与 32 位数据总线间的转换)、以及数字信号速率的不同而不同。许多逻辑 IC 能够将高电平转换成低电平(如将 5V 转换到 3.3V 逻辑),但很少能将低电平转换成高电平(如将 3.3V 转换到 5V)。逻辑电平转换可通过一个分立的晶体管或甚至是一个电阻与二极管的组合实现。但这些方法固有的寄生电容会降低数据传输速率。

尽管已有字节宽度的和字宽度的电平转换器件,但它们对本文讨论的< 20Mbps 的串行总线(SPI、I²C、USB 等)并不理想。封装尺寸大、需要使用很多引脚和 I/O 方向引脚的转换器对于小型串行总线和外设接口并不理想。

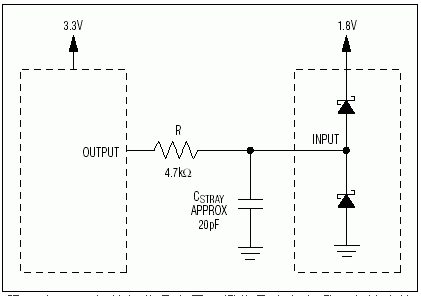

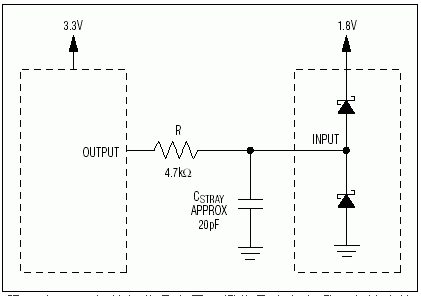

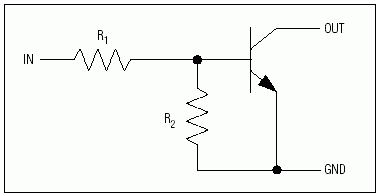

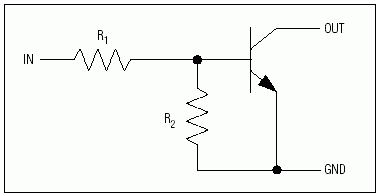

串行外设接口由单向控制线组成:数据入、数据出、时钟和片选。数据入和数据出也被称为主入从出(MISO)和主出从入(MOSI)。SPI 能够使用超过 20Mbp 的时钟信号,使用 CMOS 推挽逻辑。由于 SPI 是单向的,没有必要在同一根信号线上实现双向转换。这使电平转换变得简单一些,因为可以采用电阻与二极管(图 1)或分立 / 数字晶体管(图 2)等简单方案。

图 1. 电阻 - 二极管拓扑是在同一根信号线上实现双向转换的可选技术之一

图 2. 分立 / 数字晶体管是实现双向转换的另外一种选择

I²C、SMBus 和 1-Wire®接口为双向、漏极开路拓扑。I²C 有 3 个速度范围:≤ 100kbps 的标准模式、≤ 400kbps 的快速模式、≤ 3.4Mbps 的高速模式。双向总线的电平转换更加困难,因为必须在同一根数据线上进行双向转换。基于电阻 - 二极管或集电极 / 漏极开路的单级晶体管转换器的简单拓扑由于固有的单向性,无法满足要求。

单向高到低电平转换—输入过压容差

为了将逻辑电平由高向低转换,IC 厂商制造了大量的声称容许过压输入的器件。具有输入过压保护的逻辑器件是指能够承受(不被损坏)高于其电源电压的输入电压。这种具有输入保护的器件简化了从高 VCC 到低 VCC 逻辑的转换任务,同时又增加了信噪比裕量。

容许过压输入,例如容许 1.8V 供电的逻辑器件接受 1.8V 或更高的逻辑电平输入。LVC 逻辑系列的器件,大部分是输入过压保护的,在需要由高向低转换的应用中表现良好。但是,相反的情况,由低到高的转换并不如此简单。由低电压逻辑产生高电压逻辑的域值电平(VIH)不切实际。

当设计的电路由于连接器、高扇出和杂散电容导致高负载电容时,应注意,对于所有逻辑系列,降低电源电压也会降低驱动能力。但在 3.3V 的 CMOS 或 TTL (LV、LVT、ALVT、LVC 和 ALVC)与 5V 标准 TTL (H、L、S、HS、LS 和 ALS)之间是一个例外。在这些逻辑系列中,3.3V 和 5V 逻辑的触发点(VOL、VIL、VIH、VOH)相互匹配。

低 - 高和高 - 低混合转换

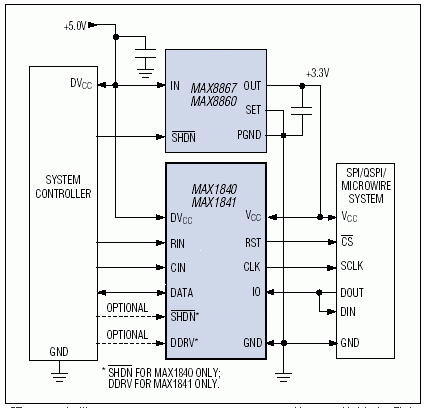

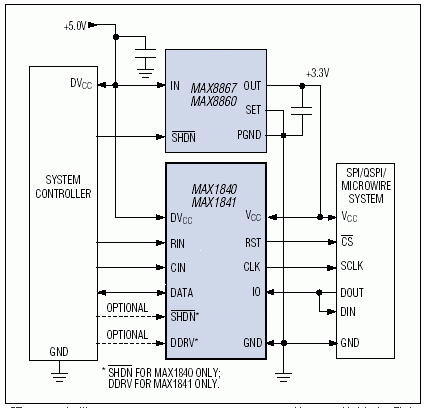

诸如 SPI 总线类的应用要求低 - 高和高 - 低混合电平转换。例如,在工作于 1.8V 的处理器和工作于 3.3V 的外设之间。尽管可以使用以上方案进行组合,但也可使用单个芯片,如:MAX1840、MAX1841 或 MAX3390 满足需求(图 3)。

图 3. 一个带 SPI/QSPI™/MICROWIRE™接口、能够实现高 - 低和低 - 高混合转换的 IC 电平转换器示例

其它系统,如 I²C、1-Wire 总线,需要双向的逻辑转换。基于集电极或漏极开路单晶体管的简单拓扑,由于固有的单向性,不能工作于双向总线。

双向收发器方式

对于更大型的字节或字宽度总线而言,由于已有 WR 和 RD 信号,在不同逻辑电平之间传递数据的方法之一是使用如 74CBTB3384 类的总线开关器件。这类器件专门针对在 3.3V 和 5V 之间的电压下工作进行了优化。对小型的 1 线或 2 线的总线,这种方法有两个问题。首先,需使用独立的使能引脚控制数据传输方向,这会占用宝贵的端口引脚资源。其次,需要使用大型 IC,会占用宝贵的电路板空间。

所有的方案都有其优缺点,但设计者需要一款通用器件,能工作于所有电平,允许低到高和高到低的混合转换,还包括进行单向和 / 或双向转换。下一代双向电平转换器(MAX3370–MAX3393 IC 系列的 MAX3370)既能满足这些要求,还能克服使用其它方案带来的问题。

MAX3370 使用一种传输门方法实现电平转换(图 4),依赖外部输出驱动器吸收电流,无论是工作在低电压还是高电压逻辑范围。这使该器件既能与漏极开路也能与推挽式输出级一起工作。而且,传输门相对较低的导通电阻(小于 135Ω)对转换速率的影响远小于图 1 中串接的电阻。

图 4. MAX3370 使用一种传输门方法实现电平转换

图 4 所示的电路还有另外两个优势。首先,对漏极开路拓扑,MAX3370 使用一个 10kΩ的上拉电阻与“加速”开关并联,最大程度降低了对外接上拉电阻的要求,同时还降低了与传统漏极开路拓扑有关的 RC 时间常数斜率。其次,MAX3370 的微型 SC70 封装还能节省宝贵的电路板空间。

解决速率问题

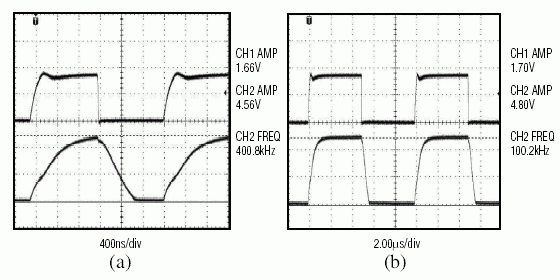

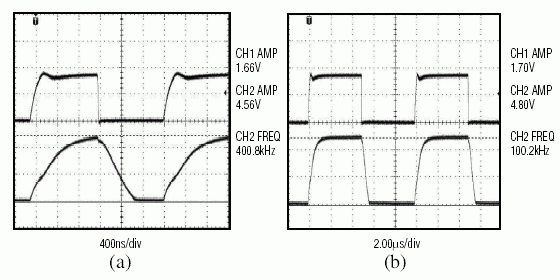

对其它大多数漏极开路方案,RC 时间常数都会限制有效数据速率(图 5 和图 6)。MAX3370 IC 系列包括一个加速机构,主动拉升上升沿,从而最大程度降低了容性负载的影响,如图 7、图 8 和图 9 所示。当输入超过预定义的门限时,器件主动拉升上升沿,从而最大程度降低由外部寄生元件引起的偏斜。这使其能够转换由推挽驱动器产生的数据速率最高达 20Mbps 的信号。对源自漏极开路驱动器的信号转换速率低一些。对于其它的漏极开路拓扑,可通过外接上拉电阻提高速率。

图 5. 20kHz 单 FET 漏极开路输出波形图,表明 RC 时间常数会对数据速率产生影响

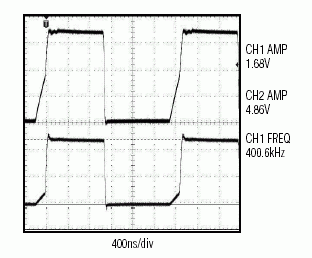

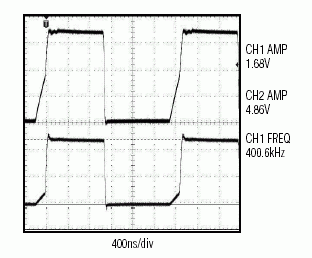

图 6. 双晶体管收发器分别以 400kHz (a)和 100kHz (b)速率将 1.8V 转换成 5V 的波形图,表明有效数据速率受到了限制

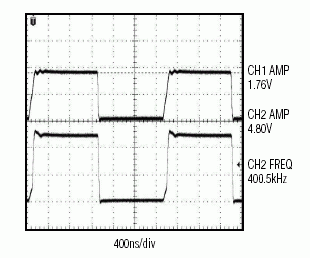

图 7. MAX3370 以 400kHz 速率将 1.8V 转换成 5V 的输出波形图,容性负载效应被大幅度降低了

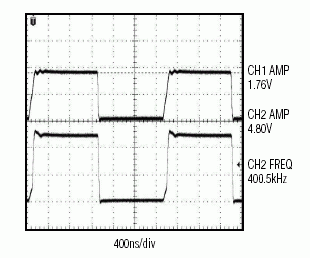

图 8. MAX3370 使用一个 4.7kΩ上拉电阻以 400kHz 速率输出的波形图,容性负载效应被大幅度降低了

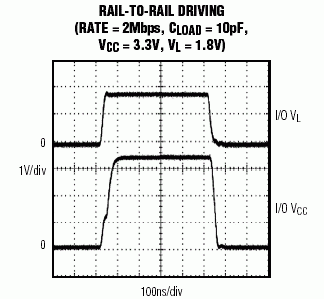

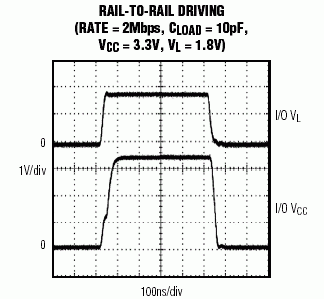

图 9. 此图是一个 MAX3370 高速测试电路满幅驱动输出的例子

解决通用电压问题

应用中理想要求是单独一个元件能以任何速度转换任意两种逻辑电平。MAX337x 系列的 IC 是为低至 1.2V 高至 5.5V 的逻辑电平所设计。一个芯片就能提供在大多数应用中需要的电平转换,而不需针对每一种电平转换都选择一种逻辑器件。

以前,在同一个电路中实现低到高和高到低的电平转换只能使用独立的芯片。现在,MAX337x 系列双向、拓扑无关(推挽和漏极开路)的一个单独芯片即可解决这两个问题。MAX3370 是一个单线、通用电平转换器。如需转换更多数量的 I/O 信号线,请参考表 1 中列出的器件。

随着每个系统中 I/O 电压种类的增多,对电平转换技术的需求更加紧迫。而负载电容,VCC 电压幅度差异,数据速率等使问题更加复杂化。对于高到低的电平转换,如果转换电压差异较小,而且有成品器件可用(如容许过压输入的逻辑 IC),问题则不太严重。

但是,能处理较大 VCC 电压差异和能将低电平转换成高电平的 IC 或分立元件电路就比较困难了。双向和漏极开路拓扑并不很适合高速率数据。Maxim 的电平转换器降低了在宽电压范围内单 / 双向、推挽和漏极开路拓扑电平间转换的难度。这些 IC 提供极小的封装,标准应用中不需任何外部元件。

烜芯微专业制造二极管,三极管,MOS管,桥堆等20年,工厂直销省20%,4000家电路电器生产企业选用,专业的工程师帮您稳定好每一批产品,如果您有遇到什么需要帮助解决的,可以点击右边的工程师,或者点击销售经理给您精准的报价以及产品介绍

烜芯微专业制造二极管,三极管,MOS管,桥堆等20年,工厂直销省20%,4000家电路电器生产企业选用,专业的工程师帮您稳定好每一批产品,如果您有遇到什么需要帮助解决的,可以点击右边的工程师,或者点击销售经理给您精准的报价以及产品介绍