MOS集成电路中的寄生效应

在MOS集成电路中,除了电路设计中需要的MOS管外,还存在着一些不需要的寄生MOS晶体管和电容,它们将给集成电路的正常工作带来不利的影响,下面将介绍这些MOS集成电路中的寄生效应。

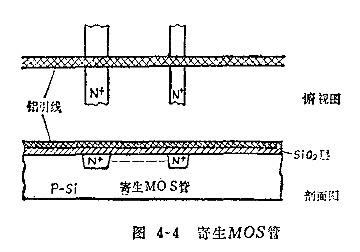

(1)寄生MOS管

MOS集成电路中,当电路铝引线串过两个扩散区时(例如地铁式布线),就在这条铝引线之下形成一个寄生MOS管。如图4-4所示。

图中衬底为P型硅,扩散区为N+,当铝引线上加正电压并当正电压高于开启电压时,在两个N+扩散区之间即形成寄生的N-MOS管。

两个扩散区本来是两条不同的电路引线,结果被寄生MOS管所连通。可见寄生MOS管会给电路带来不良影响。

为了防止寄生MOS管效应,在集成电路设计时,要尽量避免铝引线横跨两个扩散区,必不可免时,也要加大扩散区间隔,以减小寄生MOS管的宽长比,增大它的导通电阻。

或者在工艺上增加二氧化硅层的厚度,使得正常运用时寄生MOS管不至导通。

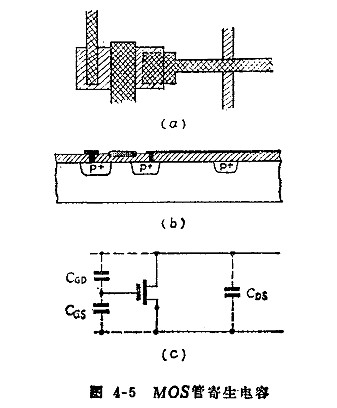

(2)寄生电容

MOS集成电路中的寄生效应:MOS集成电路中除了MOS管本身具有的MOS电容外,还存在着一些寄生电容,主要寄生电容有Cgs: MOS管栅极与源区之间寄生电容。Cgd: MOS管栅极与漏区的寄生电容。

这是由于栅极金属要交叠覆盖一部分源漏区而形成的(参见图4-5( b)),其数值大约为0.03PF/μm°。

另一种寄生电容是源漏极之间的Cds。 Cds包括寄生MOS管电容;源漏区对衬底的PN结电容和金属引线与扩散区之间的电容。寄生电容中对MOS管特性影响最大的是栅极与漏极之间的寄生电容Cgd,因为它会对信号起负反馈作用(参见图4-5(c))。

(3)MOS集成电路中的衬底效应

MOS集成电路中的寄生效应:在MOS晶体管中,通常源极是和衬底接在一起的,它们具有相同的电位。

但是,在MOS集成电路中,所有的MOS管都是制作在同一衬底硅片之上的,衬底是公共的。显然各个MOS管的源极不可能全与衬底相连,否则就会造成部分MOS管的短路,影响构成电路。

MOS集成电路中,衬底接在一定电位上( N-MOS衬底接电路中最低电位点,P-MOS衬底接电路中最高电位点),以保证各MOS管之间的“隔离”。

这样就使得MOS集成电路中某些MOS管的衬底电位与源极电位不再相同了,形成了衬底与源极之间偏压VBS。

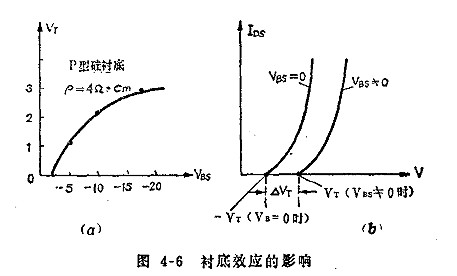

很显然,VBS是这些MOS管衬底与源极之闻的反向偏压。故源极与衬底之间的耗尽层比村底与源极相连时要加宽。从而造成MOS管开启电压的变化。以N-MOS反相器为例,开启电压Vr与衬源偏压VBS之间关系如图4-6所示。

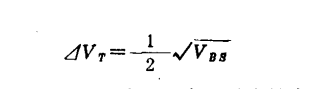

从图中可以看出,对N-MOS管衬源电压VBS增加时,开启电压Vr也要加大。在电路设计上VBS对开启电压变化量⊿Vr的影响可以用下面近似公式估算:

需要指出:MOS集成电路中存在衬底效应并不是一件坏事,恰当地利用衬底效应可以制造出增强型MOS管。

因为选用低电阻率(高掺杂)的P型硅片制造N型增强型MOS管会增加各扩散区的势垒电容,影响电路工作速度,而选用高电阻率的P型硅;

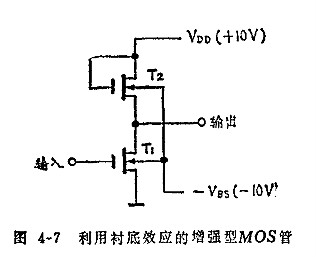

由于工艺上难以使二氧化硅层中的正电荷(例如钠离子沾污)完全消除,因而很难形成增强型MOS管在MOS集成电路中,衬底不接地电位,而是接在另外一个负电源上,这样衬底与管子源极之间就存在着一个负电压(如图4-7所示),使管子获得一个开启电压值,从而得到增强型N-MOS管。

烜芯微专业制造二极管,三极管,MOS管,桥堆等20年,工厂直销省20%,4000家电路电器生产企业选用,专业的工程师帮您稳定好每一批产品,如果您有遇到什么需要帮助解决的,可以点击右边的工程师,或者点击销售经理给您精准的报价以及产品介绍