MOS管知识-mosfet体效应(衬偏效应)详解

mosfet体效应(衬偏效应)详解

关于MOSFET的体效应(body-effect,衬底调制效应/衬偏效应),主要是来源于mos管的S-B(Source-Bulk)端之间的偏压对MOSFET阈值电压vth的影响:以NMOS为例,当晶体管的源端(Source)电势高于体端(Bulk)电势时,栅下面的表面层中将有更多的空穴被吸引到衬底,使耗尽层中留下的不能移动的负离子增多,耗尽层宽度增加,耗尽层中的体电荷面密度Qdep也增加。

而从一般的MOSFET的阈值电压的关系式中Vth与Qdep的关系(可以考率Vth为MOS栅电容提供电荷以对应另一侧耗尽区固定电荷的大小),可以看到阈值将升高。

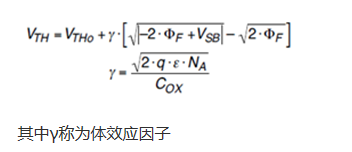

在考虑体效应之后,MOS管的阈值电压可以写为:

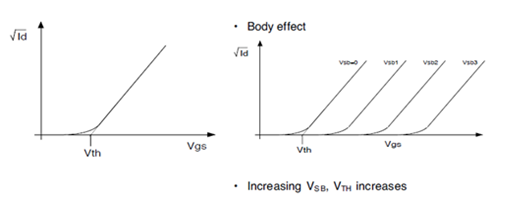

我们亦可以在下图直观的了解VSB对Vth的影响:

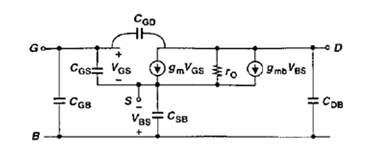

相应的,由于体效应的存在,在MOSFET的小信号模型中,需要在gm*VGS的电流源旁并联一个大小为gmb*VBS的电流源

MOSFET的体效应(衬偏效应)

MOSFET的工作是通过在半导体表面产生导电沟道—表面反型层来进行的,因此器件中存在一个由栅极电压所诱生出来的p-n结—场感应结。一旦出现了沟道,则沟道以内的耗尽层厚度即达到最大,并保持不再变化(栅电压不再能够改变耗尽层厚度)。

(1)什么是衬偏效应?

对于MOS-IC而言,在电路工作时,其中各个MOSFET的衬底电位是时刻变化着的,如果对器件衬底的电位不加以控制的话,那么就有可能会出现场感应结以及源-衬底结正偏的现象;一旦发生这种现象时,器件和电路即告失效。所以,对于IC中的MOSFET,需要在衬底与源区之间加上一个适当高的反向电压——衬偏电压,以保证器件始终能够正常工作。简言之,衬偏电压就是为了防止MOSFET的场感应结以及源结和漏结发生正偏、而加在源-衬底之间的反向电压。 由于加上了衬偏电压的缘故,将要引起若干影响器件性能的现象和问题,这就是衬偏效应(衬偏调制效应),又称为MOSFET的体效应。

这种衬偏电压的作用,实际上就相当于是一个JFET的功能——沟道-衬底的场感应p-n结作为栅极控制着输出电流IDS的大小。所以,对于加有衬偏电压的MOSFET,从工作本质上来说,可看成是由一个MOSFET和一个JFET并联而成的器件,只不过其中JFET的作用在此特别称为MOSFET的体效应而已。这就是说,加上衬偏电压也就相当于引入了一个额外的JFET。

(2)衬偏效应对器件性能的影响: ①MOSFET在出现沟道(反型层)以后,虽然沟道下面的耗尽层厚度达到了最大(这时,栅极电压即使再增大,耗尽层厚度也不会再增大);但是,衬偏电压是直接加在源-衬底之间的反向电压,它可以使场感应结的耗尽层厚度进一步展宽,并引起其中的空间电荷面密度增加,从而导致器件的阈值电压VT升高。而阈值电压的升高又将进一步影响到器件的IDS及其整个的性能,例如栅极跨导降低等。 衬底掺杂浓度越高,衬偏电压所引起的空间电荷面密度的增加就越多,则衬偏效应越显著。例如,p阱-CMOS中的n-MOSFET,它的衬偏效应就要比p-MOSFET的严重得多。

②由于衬偏电压将使场感应结的耗尽层厚度展宽、空间电荷面密度增加,所以,当栅极电压不变时,衬偏电压就会使沟道中的载流子面电荷密度减小,从而就使得沟道电阻增大,并导致电流减小、跨导降低。 ③当MOSFET在动态工作时,源极电位是不断在变化着的,则加在源-衬底之间的衬偏电压也将相应地随着而不断变化;这就产生所谓背栅调制作用,即呈现出一定JFET的功能。 ④由于衬偏电压会引起背栅调制作用,使得沟道中的面电荷密度随着源极电位而发生变化,即产生了一种电容效应,这个电容就称为衬偏电容。衬偏电容的出现即将明显地影响到器件的开关速度。

⑤由于MOSFET在加有衬偏电压时,即将增加一种背栅调制作用,从而就额外产生出一个与此背栅调制所对应的交流电阻;于是,这就将使得器件的总输出电阻降低,并导致电压增益下降。所以,减小衬偏效应将有利于提高电压增益。(3)减弱或消除衬偏效应的措施: ①把源极和衬底短接起来,当然可以消除衬偏效应的影响,但是这需要电路和器件结构以及制造工艺的支持,并不是在任何情况下都能够做得到的。

例如,对于p阱CMOS器件,其中的n-MOSFET可以进行源-衬底短接,而其中的p-MOSFET则否;对于n阱CMOS器件,其中的p-MOSFET可以进行源-衬底短接,而其中的n-MOSFET则否。 ②改进电路结构来减弱衬偏效应。例如,对于CMOS中的负载管,若采用有源负载来代替之,即可降低衬偏调制效应的影响(因为当衬偏效应使负载管的沟道电阻增大时,有源负载即提高负载管的VGS来使得负载管的导电能力增强)。

烜芯微专业制造二极管,三极管,MOS管,桥堆等20年,工厂直销省20%,4000家电路电器生产企业选用,专业的工程师帮您稳定好每一批产品,如果您有遇到什么需要帮助解决的,可以点击右边的工程师,或者点击销售经理给您精准的报价以及产品介绍

烜芯微专业制造二极管,三极管,MOS管,桥堆等20年,工厂直销省20%,4000家电路电器生产企业选用,专业的工程师帮您稳定好每一批产品,如果您有遇到什么需要帮助解决的,可以点击右边的工程师,或者点击销售经理给您精准的报价以及产品介绍