MOS管逻辑电路-分析重点:

1.MOS管构成的缓冲器Buffer和漏极开路们OD门是数字电路非常重要的概念,怎么构成的?

2.反相器,线与逻辑怎么玩, 又怎么用呢?

3.根据原理图,真值表,应用典型电路全面了解基本的逻辑门,与门,或门,与非门。

4.导体SS, TT, FF是怎么回事?

MOS管逻辑电路(与门,或门,非门等)

作为硬件工程师,不能不懂芯片;而要想懂芯片,MOS管构成的各种基本逻辑电路必须熟记于心,才能够更熟练的看懂芯片的框图。场效应管(Field-Effect Transistor)通过不同的搭配可以构成各种各样的门电路,如开篇所说,这些最基本的单元电路或许是现代IC的基础。以下的电路形式在常用的74系列的芯片中大量存在着,之后介绍的OD门,缓冲器则常见于芯片的GPIO口等管脚的设计。

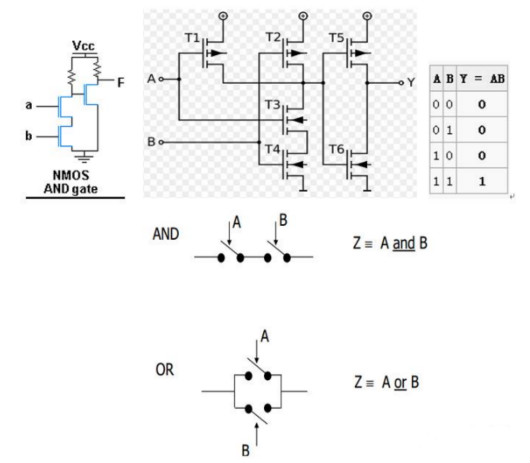

MOS管构成基本的与门、或门电路

与门可以由六个管子构成,通过示意图应该能更清楚看出与门的工作示意图,然后由真值表可以看出输入输出的对应关系。本文中给出与门的对应电路,如有兴趣,大家可以思考或门的电路结构,其实二者是存在对应关系的。

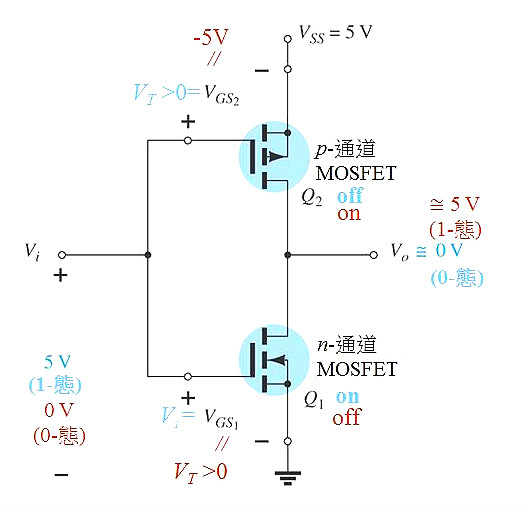

2. 反相器

下图则给出了反相器的电路图,输入和输出状态相反,谓之反相器。

电路分析:

输入Vi为低电平时,上管导通,下管截止,输出为高电平;输入Vi为高电平时,上管截止,下管导通,输出为低电平。

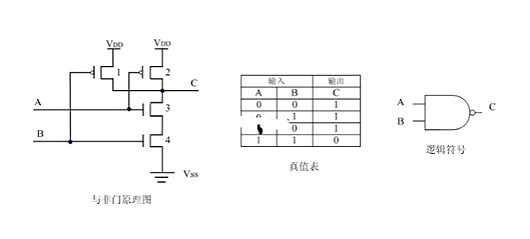

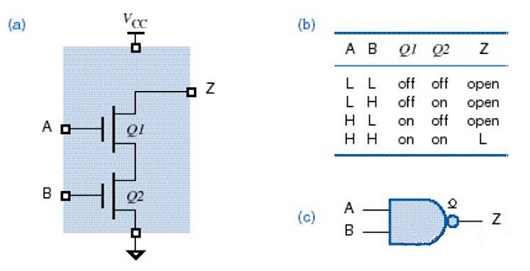

与非门

下图则给出了与非门的电路图,与非门也就是同为零,异为一。

当A,B输入均为低电平时,1,2管导通,3,4管截止,C端电压与Vdd一致,输出高电平。当A输入高电平,B输入低电平,1,3管导通,2,4管截止,C端电位与1管的漏极保持一致,输出高电平。

当A输入低电平,B输入高电平,2,4导通,1,3管截止,C端电位与2管的漏极保持一致,输出高电平。当A,B输入均为高电平时,1,2管截止,3,4管导通,C端电压与地一致,输出低电平。

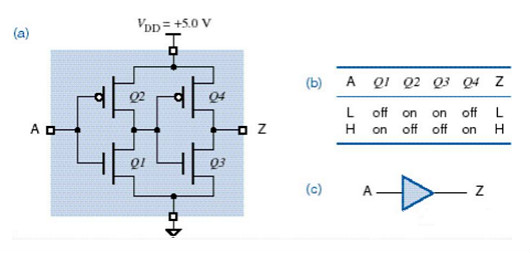

4. 缓冲器Buffer

电路分析:

前面一级Q1,Q2组成了一个反相器;后面一级Q3,Q4又构成了一个反相器,相当于反了两次相,于是又还原了。

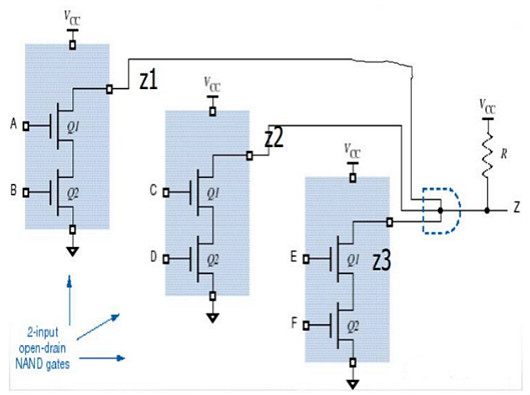

5. 漏极开路门

漏极开路门是一个十分经典常用的电路,常见于主芯片的GPIO口或者单片机的GPIO口的设计中。最重要的一点就是:漏极开路是高阻态,一般应用需要接上拉电阻。

【漏极开路门的应用-线与逻辑】

“线与”逻辑是因为多个逻辑单元的输出的三极管,共用一个上拉电阻,只要一个逻辑单元输出低电平,即集电极(漏极)开路输出的管子导通,那么输出低电平;而只有全部单元截止,输出端被上拉电阻置为高电平,这是一个很实用的电路,可以用于逻辑仲裁等电路系统中。

烜芯微专业制造二极管,三极管,MOS管,桥堆等20年,工厂直销省20%,4000家电路电器生产企业选用,专业的工程师帮您稳定好每一批产品,如果您有遇到什么需要帮助解决的,可以点击右边的工程师,或者点击销售经理给您精准的报价以及产品介绍

烜芯微专业制造二极管,三极管,MOS管,桥堆等20年,工厂直销省20%,4000家电路电器生产企业选用,专业的工程师帮您稳定好每一批产品,如果您有遇到什么需要帮助解决的,可以点击右边的工程师,或者点击销售经理给您精准的报价以及产品介绍