硅栅MOS结构详细解析

硅栅MOS结构:在MOS-IC的早期产品中,广泛使用金属AI作为栅极。例如上世纪60年代中期第一只MOS-IC即为p沟增强型A1栅器件。但随着MOS-IC规模的增大、线条的变细性能要求的提高,Al栅MOS技术逐渐被硅栅MOS所代替。

硅栅MOS结构:工艺的特点

硅栅工艺的发展和应用,同以下几个方面的原因紧密相连:

(1)我们知道Al栅的淀积必须在完成了硅器件所有的高温过程以后进行。因此它务必要同IC中器件的源、漏区对准。在套准精度的限制之下,棚区的尺寸必须比预定的沟道长度更长,以便覆盖住源、漏区。

这导致了集成密度的下降和寄生效应的增加。由于多晶硅与硅衬底是同一种材料,具有相同的熔点,它可以在形成漏、源区之前淀积上去。同时硅栅本身又可作为离子注入的掩膜,几乎可完美地形成所需的器件沟道区。

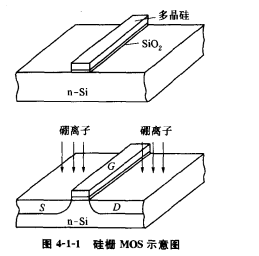

这种“自对准”的特点不仅简化了制备工艺,而且增加了器件密度,减少了栅-源间和栅-漏间的寄生电容。这一特点的示意图如图4-1-1所示。在硅衬底上先要形成薄的栅氧化区,随后淀积多晶硅并图形化,随后经由离子注入形成漏、源区。在硅栅之下没有注入离子,形成所需的沟道。

(2)由于硅栅与硅衬底之间的接触功函数的差别为零,从而使阈值电压负得更少一点,减少了p沟MOS的阈值电压绝对值。如可从-4V下降为-2V。这样使硅栅MOSIC可以同其他数字电路相兼容,如TTL电路等。

(3)由于多晶硅能忍受高温,它可以完全地被SiO2层封包起来,使多晶硅不仅能作为栅电极用,而且可以作为互连线用。在多层布线技术中,它可以被另外的金属层或多晶硅层所穿过。

使IC设计中的布线更为方便和紧凑。因多晶硅能忍受高温.它又可允许被覆盖掺磷SiO2等介质膜,以完成金属化之前所必须的表面平坦化过程。

硅栅MOS结构:硅栅MOS技术中最大的不利因素是它比Al栅材料有高得多的电阻率。即使在高掺杂的情况下,0.5μm厚的多晶硅电阻率约为20Ω/sq。这同相应厚度的Al材料相比要大约400倍。高的电阻率势必造成更长的RC时间常数以及芯片中较严重的直流电压的变化。

为克服这一缺点,常在多晶硅上淀积耐熔金属或硅化物薄膜。这类薄膜的薄层电阻率为1Ω/sq,可以明显地减少多晶硅的高阻带来的负面影响。但是,尽管存在上述的限制,硅栅MOS技术已经成为当今MOS-IC技术中的主流技术。

场区、有源区和等平面工艺

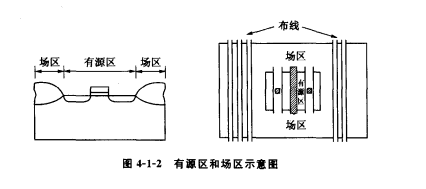

在MOS-IC的芯片内,从工艺结构来看,可以分为两个区域:场区和有源区。有源区是用以制作MOS晶体管、电阻或电容的区域。在此区域内不存在很厚的热生长SiO2 层,只存在制作器件必须的薄氧化层和当隔离介质中的CVD淀积的SiO2层。

在此区域内,除器件所必须的引出线外,一般不能通过其他导电层。在有源区之外的就是场区,这一区域由很厚的热生长SiO2层组成,大量的金属布线穿越其间,芯片的众多金属引线脚也布置在它上面。图4-1-2是有源区和场区的示意图。

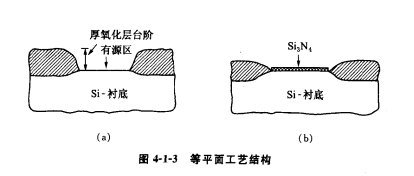

在普通的集成电路平面工艺中,SiO2层作为绝缘介质和掺杂时的掩蔽材料,发挥了关键的作用。MOS-IC的场区由热生长SiO2层组成,而有源区则无这样的厚氧化层。热生长SiO2层的过程,要消耗硅衬底材料。

在形成有源区时,必须将有源区上的厚SiO2层除去。这样,在有源区和场区之间形成一个明显的台阶, 如图4-1-3所示。这样的高台阶对从有源区引出的布线是不利的,金属布线在台阶处容易断裂,造成器件的失效。

用“等平面工艺”很容易解决这一问题。只要在有源区的区域上淀积一层Si3N4以保护这一区不被热氧化,从而使这一区域的硅平面和四周的厚氧化层平面维持在较接近的水平,大大减少了布线跨越的台阶。一种叫全凹陷氧化工艺(FUROX)提供了较完美的等平面氧化技术。

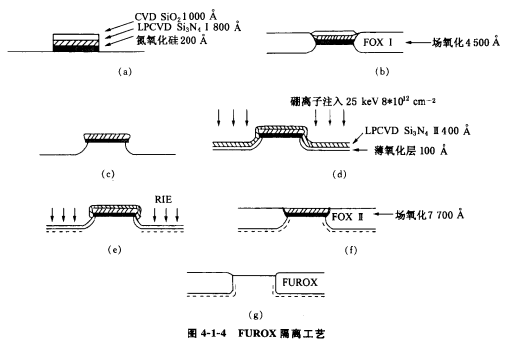

图4-1-4示出了这一工艺的主要步骤。在有源区部分依次热生长氮氧化硅层200A,LPCVD生长Si3N4 800A,CVD淀积SiO2 1000A。随后在场区热生长siO2 4500A。然后用化学腐蚀方法除去以形成一个槽。

生长第二层100A厚的氧化硅层并用CVD方法淀积400A厚的氮化硅层。进行自对准场区的“沟道阻止”硼注入。用离子反应刻蚀方法各向异性地腐蚀掉第二层氮化硅层,但仍保留侧墙处的Si3N4层以作为掩蔽氧化用。接着进行第二次场氧化,形成一个无缺陷,接近“零鸟嘴”,全凹陷的非常平坦的氧化区。