MOS晶体管的最高频率

MOS晶体管在工作频率增高到一定值以后,它的特性就将随着频率的增高而变坏。

MOS管的最高频率,大家知道,MOS晶体管的沟道区隔着绝缘的氧化层,在这一氧化层上面覆盖者金属栅电极,于是就形成了以氧化物为介质的平板电容器,称为栅电容,用符号Cg表示。

如果在某一时刻输入信号的变化使Vg增加时,沟道中感生的载流子将增多。这些感生载流子的增多过程也就是栅电容的充电过程。充电是通过MOS管的通导电阻Ron进行的,其充电时间常数为t=RonCg;而当Vg减小时,Cg就要通过Ron放电。

当输入信号的周期比栅电容通过Ron充放电的时间常数长很多时(低频情况),栅电容的充放电过程就进行得很充分,输出信号就完全能够跟上输入信号的变化。这时,MOS晶体管的放大性能将不会受到影响。

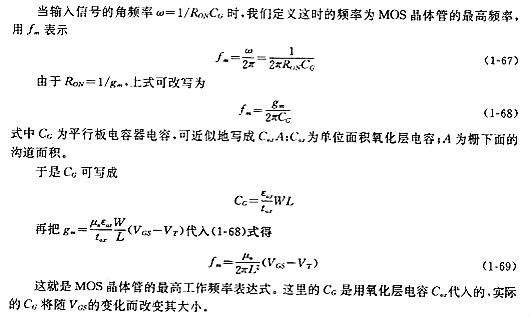

但是,当输入信号的周期比栅电容充放电的时间常数还小,也就是输入信号的角频率ω比MOS管的固有频率高时,即ω> 1/RonCg。这样,栅电容的充放电过程就进行得不够充分,输出信号就不能完全跟上输入信号的变化。此时,MOS晶体管的放大特性就要变坏。

从(1-69)式中看到,MOS管的最高频率,与沟道长度的平方成反比。可见,要提高MOS管的最高频率,沟道长度L就必须设计得短一点。另外fm与μ成正比。由于电子迁移率比空穴迁移率大,所以在其它条件相同的情况下,N沟道MOS晶体管的高频性能要比P型沟道MOS晶体管要好。

为了对fm有一个定量的概念,下面举一个例子。

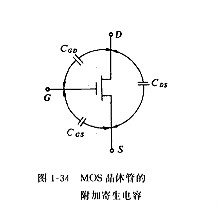

这是一个频率相当高的器件。实际上,在MOS电路里的晶体管,其最高频率最少也要低2~3个数量级。这是因为存在许多寄生电容。

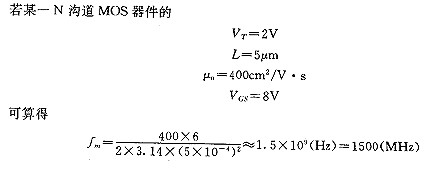

其中有金属栅与源极扩散区交叠造成的栅源覆盖电容Cgs(还包括引线间的分布电容)、栅和漏之间的附加寄生电容Cgd;另外还有漏极与P型基片间的PN结电容和其他寄生电容,将构成漏和源间的附加寄生电容Cds。这些电容附加到MOS晶体管之上(如图1-34),将使器件频率特性进一步变坏。

在MOS集成电路里,除了MOS晶体管的电容外,还有其他一些寄生电容,在电路中起很大作用。这是MOS集成电路速度低的原因所在。图1-35表示MOS集成电路中各类寄生电容示意图,其中:

晶体管参数-频率特性

晶体管的电流放大系数与工作频率有关。若晶体管超过了其工作频率范围,则会出现放大能力减弱甚至失去放大作用。晶体管的频率特性参数主要包括特征频率fT和最高振荡频率fM等。

1.特征频率fT:晶体管的工作频率超过截止频率fβ或fα时,其电流放大系数β值将随着频率的升高而下降。特征频率是指β值降为1时晶体管的工作频率。

通常将特征频率fT小于或等于3MHZ的晶体管称为低频管,将fT大于或等于30MHZ的晶体管称为高频管,将fT大于3MHZ、小于30MHZ的晶体管称为中频管。

2.最高振荡频率fM:最高振荡频率是指晶体管的功率增益降为1时所对应的频率。

通常,高频晶体管的最高振荡频率低于共基极截止频率fα,而特征频率fT则高于共基极截止频率fα、低于共集电极截止频率fβ。

MOS晶体管的最高工作频率

MOS晶体管的最高工作频率被定义为:当对栅极输入电容Cgc的充放电电流和漏源交流电流的数值相等时,所对应的工作频率为mos晶体管的最高工作频率。

这是因为当栅源间输入交流信号时,由源极增加(减少)流入的电子流,一部分通过沟道对电容充(放)电,一部分经过沟道流向漏极,形成漏源电流的增量。因此,当变化的电流全部用于对沟道电容充放电时,晶体管也就失去了放大能力。

烜芯微专业制造二极管,三极管,MOS管,桥堆等20年,工厂直销省20%,4000家电路电器生产企业选用,专业的工程师帮您稳定好每一批产品,如果您有遇到什么需要帮助解决的,可以点击右边的工程师,或者点击销售经理给您精准的报价以及产品介绍

烜芯微专业制造二极管,三极管,MOS管,桥堆等20年,工厂直销省20%,4000家电路电器生产企业选用,专业的工程师帮您稳定好每一批产品,如果您有遇到什么需要帮助解决的,可以点击右边的工程师,或者点击销售经理给您精准的报价以及产品介绍