高功率激光二极管(HPLD)是发展最快的激光器类别之一,其快速发展背后的主要驱动力,来源于光纤激光器对泵浦源的需求激增;目前光纤激光器已经成为材料加工应用的首选工具。此外,HPLD还广泛应用于光动力学治疗、美容手术和组织外科手术等医学领域,以及直接用于材料加工中,包括熔覆、3D打印、切割和焊接等应用。

HPLD的另一个应用领域是国防工业,在这个细分领域其增长驱动力主要来自对定向能武器的需求。HPLD能提供的400~2000nm的波长范围,是任何其他类型的激光器所无法比拟的;其能提供的输出功率范围为从1W到300W以上,同时能在极为紧凑的体积下实现高达65%的光电转换效率。[1]目前,单管能在0.5mm×5mm的外观尺寸下,提供高达20W的可靠功率输出。[2]

HPLD由于具备上述一系列独特性能,因此非常适用于很多正在不断增长的广泛应用领域。分析师Nilushi Wijeyasinhe博士的一篇题为《2019-2029激光二极管和直接二极管激光器:技术、市场和预测》的报告显示:到2029年,全球激光二极管和直接二极管激光器的市场规模将达到139.85亿美元,其中激光二极管占119.52亿美元,直接二极管激光器占20.33亿美元。

关键工艺挑战

芯片贴合工艺是HPLD制造中最关键的封装工艺。在这个过程中,通常采用金锡(AuSn)共晶键合工艺,将单管或巴条形式的HPLD芯片贴合到热沉衬底上。芯片贴合工艺对HPLD的光学效率和可靠性起着至关重要的作用。芯片贴合工艺所面临的主要挑战主要包括如何保障:高精度、共晶质量、空隙率、共面性,以及如何实现高混合、大批量生产。

在芯片或巴条的发射前端面和热沉衬底的边缘之间,有着极高精度的定位要求。通常,芯片贴装工艺完成后,芯片的前端面到衬底边缘之间,不应有凹痕;并且芯片端面突出衬底边缘的部分,要小于5~10μm。为了实现这个目标,贴片机贴装后的芯片端面凸出衬底边缘的尺寸,通常应小于±2.5μm。激光芯片和衬底边缘的公差分别小于1μm。因此,贴片机的定位精度必须小于±1.5μm。

随着HPLD芯片功率的增加,单管变得更长,有些芯片的长宽比甚至超过了10。在这种情况下,巴条的贴装极具挑战性,因为大的贴装表面积将放大贴装后的缺陷,如空隙率和巴条倾斜角度。

定位精度1.5μm的高速贴片机

为了解决HPLD生产中面临的芯片贴装工艺挑战,需要一种超高精度的、高速、高柔性的全自动贴片机。这台机器要具备如下特性:定位精度小于±1.5μm、提供可编程的键合力、共晶阶段和均匀施力过程(在可控力的作用下,沿X、Y、Z方向的微小运动)。根据这些要求,MRSI-H-LD 1.5μm全自动贴片机应运而生。

针对HPLD芯片贴装工艺,MRSI-H-LD贴片机实现了±1.5μm@3σ的机械定位精度。同时,并行处理能力大大缩短了机器的周期时间。尽管贴装速度高度依赖于具体的应用,但是典型的贴装速度仍可达到每小时超过150个CoS(chip-on-submount)单元。

可编程的贴装头(bondinghead)具有实时闭环力反馈和调节功能,可以对III-V族半导体元件进行精细处理。例如,通过对每种组件类型所施加的力进行编程,HPLD制造商可以确保每种类型的高功率激光芯片,都可以对芯片施加经过独特编程和控制的力,进行抓取和放置。

无空隙共晶过程

除了定位精度外,回流焊工艺中的温度分布,对HPLD芯片贴装过程也至关重要。在共晶过程中,需要格外谨慎,以在芯片和热沉衬底之间形成一个薄的均匀共晶界面,使空隙最小,实现有效且均匀地散热。这就要求贴片机对整个贴装区域的共晶回流温度进行精确且均匀的控制。

HPLD的贴装过程,需要一个快速升温和快速降温的可编程均匀共晶加热阶段,并且在贴装过程中温度必须保持稳定。加热阶段还必须有混合气体保护层,以防止键合表面氧化,并且在冷却时界面具有最小的空隙。

例如,贴片机提供一个独特的脉冲加热快速共晶键合阶段,该阶段处于保护气体之下,保护气体中含有90%~95%的氮氢混合物,用于防止键合表面氧化。使用共晶组合,使共晶键合工艺温度最小化,通常为315°C左右。加热阶段可编程到400°C,衬底的温度保持均匀。加热阶段是为了长期稳定性而设计的。

一种独特的可编程均匀施力解决方案,解决了共面性难题,在将芯片贴装到衬底上的过程中,以通过向一个器件施加垂直力和水平力及运动的方式,来最小化键合空隙。一个用于定制化XYZ-theta的库,可以在不同的芯片和衬底条件下实现共面性,提供近乎无空隙的过程控制。

共面控制

HPLD芯片或巴条与热沉衬底之间的共面性非常重要,因为它会影响空隙率和诱导应力。因此,缺乏共面性会影响HPLD的性能和可靠性。

如果没有良好的共面性控制,由于贴装后的残余应力在巴条中的积累,巴条可能会产生翘曲,这通常被称为“smile效应”,[3]并且较长的芯片可能会产生不均匀散热,从而在沿单管的长度上产生热应力。因此,不同尺寸的单管芯片或激光巴条芯片,需要不同的键合力和精确的力控制。

特别设计的自流平(self-leveling)工具提高了键合力的均匀性,并且能挤出空气减少空隙。通过在整个芯片表面施加均衡的键合力,可以产生几乎无空隙的共晶键合,从而提供较高的芯片剪切强度和改进的共面性。

动态工具转换

目前,HPLD行业正处于转型期,由于缺乏标准化,制造商必须要面对不同外观的产品增长以及由此所带来的复杂性。不同供应商所设计的HPLD——CoS和BoS(bar-on-submount),呈现出多种不同的形式。因此,对于HPLD制造而言,高混合率的产品生产是一项极大的挑战,因为HPLD的封装设计必须面对许多不同的外观形式,以满足不同的应用需求。

MRSI-H-LD贴片机能够在不停机的情况下,动态转换工具,以处理不同形状、不同尺寸的零件。该系统提供了业界领先的生产能力和灵活性,能够在一台机器上能够实现CoS、BoS、chip on C-mount以及其他HPLD封装工艺。

利用玻璃芯片对MRSI-H-LD贴片机进行了性能测试,并验证了设备的精度。实验内容包括测量CoS和BoS芯片贴装工艺的位置精度、测量HPLD巴条的平坦度,以及用扫描声学显微镜(SAM)测量空隙率。

基于15个数据点的样本情况,实验结果显示,在X方向和Y方向的放置精度分别小于1μm@3σ和0.5μm@3σ(见图1)。此外,MRSI-H-LD贴片机还具有倒装芯片功能,能够完成P侧向上和P侧向下的处理。

图1:实验测试显示,MRSI-H-LD贴片机在X方向和Y方向的放置精度分别小于1μm和0.5μm(@3σ)。

CoS

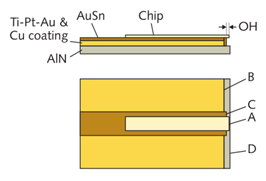

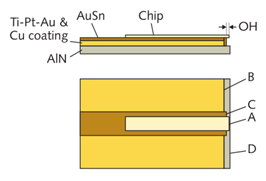

对于典型的P侧向上的CoS芯片贴装的工艺要求,如图2所示,CoS芯片贴装中的关键尺寸是激光芯片相对于AuSn涂层的凸出量,即图2中OH的尺寸,也就是下面的俯视图中所显示的A的边缘(单管的端面边缘线)到C的边缘(AuSn表面线)的距离。对10个CoS进行测试的结果表明,贴装精度小于±3μm @3σ,无凹陷,凸出量OH小于4μm。

图2:对于典型的P侧向上CoS芯片贴装的工艺要求,最关键的一个尺寸参数是OH,即A的边缘(单管的端面边缘线)到C的边缘(AuSn表面线)的距离。

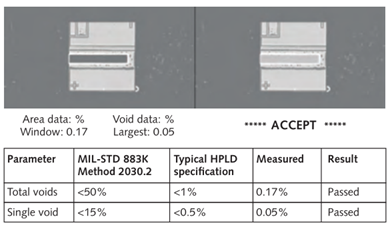

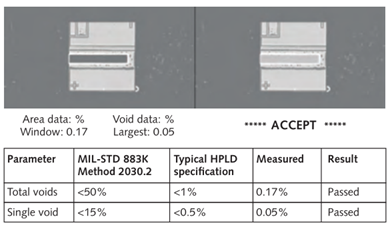

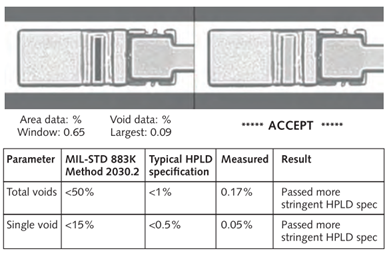

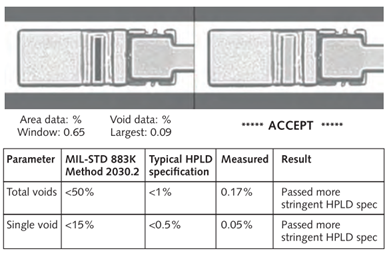

除了几何位置分析之外,为了检测焊料界面的空隙率,还使用扫描声学显微镜检测了尺寸为4mm×500μm×120μm的激光芯片样品,该芯片通过AuSn焊料贴装到AlN衬底上。贴装后空隙率远优于MIL-STD 883K Method 2030.2规范,并且还通过了更严格的HPLD空隙率规范(见图3)。

图3:CoS空隙率测试表明,贴装后的空隙率远优于MIL-STD 883K Method 2030.2规范,并且还通过了更严格的HPLD空隙率规范。

虽然放置可重复性、精度和空隙率是HPLD芯片贴装的重要性能指标,但是这些指标还必须要高速实现。典型的温度分布用于共晶芯片贴装工艺;总周期时间为23s,或每小时贴装超过150UPH(units per hour)。

Chip on C-mount

以下是在铜钨(CuW)C-mount封装中,贴装单管芯片所获得的实验结果。在实验中,尺寸为2mm×500μm×0.12μm的单管芯片,被贴装到尺寸为6.35mm×2.18mm×6.86mm(长×宽×高)的C-mount封装衬底上(预先沉积了AuSn焊料)。对9个样品的评估结果显示,芯片在C-mount封装衬底上的放置凸出量小于4.3μm@3σ,所实现的贴装后关键参数都能到达目标规范要求。

除了放置精度外,还使用SAM方法测量了焊料界面的空隙率。使用Sonoscan D-9000 C-SAM测量工具采集原始图像并进行处理,图4中给出了测量的空隙率结果。再次,在这个实验中,贴装后空隙率优于MIL-STD 883K Method 2030.2规范,并通过了更严格的HPLD空隙率规范。

图4:C-mount封装的空隙率测试表明,贴装后空隙率远优于MIL-STD 883K Method 2030.2规范,并通过了更严格的HPLD空隙率规范。

BoS

以下是将HPLD巴条芯片贴装到预沉积AuSn焊料的CuW衬底上的封装结果。实验中使用的HPLD巴条芯片的尺寸为10mm×2mm×130µm(长×宽×高),CuW衬底的尺寸为10.6mm×4.0mm×0.25mm(长×宽×高)。

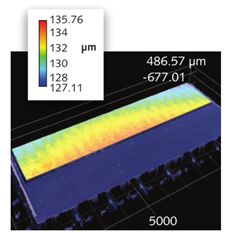

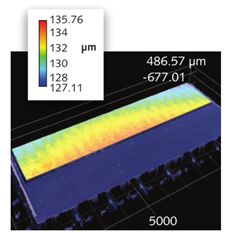

MRSI-H-LD贴片机具有一个自调平装置,它通过在整个贴装表面区域施加均匀的压力来降低smile效应,从而保持激光芯片在衬底上的共面性。所贴装的激光巴条的平坦度(见图5)表明,发射激光的前端面边缘的平坦度为130μm±1μm,或者说其机械smile范围小于2μm,这个结果对于AuSn共晶键合是可接受的。

图5:用VR50003D表面轮廓仪(由Keyence提供)测量的HPLD巴条的平坦度表明,发射激光的前端面边缘的平坦度为130μm±1μm,或者说其机械smile范围小于2μm,这个结果对于AuSn共晶键合是可接受的。

低smile效应的巴条能提供更高的光束质量,因此是所有高功率应用的一个关键指标。沿激光二极管巴条长度的线性偏移,也是一个重要的参数,因为激光二极管巴条的聚焦光束大小,会因这种偏移而变化。[4]通常,激光巴条的边到边的线性偏移应小于5μm。根据实验结果,线性偏移的测量值为3.8μm@3σ,完全符合规范要求。

总结

实验结果表明,MRSI H-LD贴片机提供了一个综合性的柔性制造系统(FMS)解决方案,解决了HPLD芯片贴装工艺面临的所有难题。该机器的芯片放置精度小于1μm@3σ,优于1.5μm@3σ的规格,CoS和Chip on C-mount封装的凸出量分别小于4μm和4.3μm。

此外,BoS的线性偏移为3.8μm,优于5μm的规格要求。空隙率测试结果表明,该机器超过了所有三种封装类型的共晶键合工艺的空隙率要求。CoS、Chip-on-C-mount和BoS封装可以在一台机器上实现。对于一个典型的CoS,贴装速度超过150UPH,其独特的功能组合为大容量和高混合HPLD封装生产,提供了一个柔性的综合性芯片贴装解决方案。

烜芯微专业制造二极管,三极管,MOS管,桥堆等20年,工厂直销省20%,4000家电路电器生产企业选用,专业的工程师帮您稳定好每一批产品,如果您有遇到什么需要帮助解决的,可以点击右边的工程师,或者点击销售经理给您精准的报价以及产品介绍

烜芯微专业制造二极管,三极管,MOS管,桥堆等20年,工厂直销省20%,4000家电路电器生产企业选用,专业的工程师帮您稳定好每一批产品,如果您有遇到什么需要帮助解决的,可以点击右边的工程师,或者点击销售经理给您精准的报价以及产品介绍