目前,在设计中使用的主要有3种电阻器:多晶硅、MOS管以及电容电阻。在设计中,要根据需要灵活运用这3种电阻,使芯片的设计达到最优。

1CMOS集成电路的性能及特点

1.1功耗低CMOS集成电路采用场效应管,且都是互补结构,工作时两个串联的场效应管总是处于一个管导通,另一个管截止的状态,电路静态功耗理论上为零。实际上,由于存在漏电流,CMOS电路尚有微量静态功耗。单个门电路的功耗典型值仅为20mW,动态功耗(在1MHz工作频率时)也仅为几mW。

1.2工作电压范围宽CMOS集成电路供电简单,供电电源体积小,基本上不需稳压。国产CC4000系列的集成电路,可在3~18V电压下正常工作。

1.3逻辑摆幅大CMOS集成电路的逻辑高电平“1”、逻辑低电平“0”分别接近于电源高电位VDD及电影低电位VSS。当VDD=15V,VSS=0V时,输出逻辑摆幅近似15V。因此,CMOS集成电路的电压电压利用系数在各类集成电路中指标是较高的。

1.4抗干扰能力强CMOS集成电路的电压噪声容限的典型值为电源电压的45%,保证值为电源电压的30%。随着电源电压的增加,噪声容限电压的绝对值将成比例增加。对于VDD=15V的供电电压(当VSS=0V时),电路将有7V左右的噪声容限。

1.5输入阻抗高CMOS集成电路的输入端一般都是由保护二极管和串联电阻构成的保护网络,故比一般场效应管的输入电阻稍小,但在正常工作电压范围内,这些保护二极管均处于反向偏置状态,直流输入阻抗取决于这些二极管的泄露电流,通常情况下,等效输入阻抗高达103~1011Ω,因此CMOS集成电路几乎不消耗驱动电路的功率。

1.6温度稳定性能好由于CMOS集成电路的功耗很低,内部发热量少,而且,CMOS电路线路结构和电气参数都具有对称性,在温度环境发生变化时,某些参数能起到自动补偿作用,因而CMOS集成电路的温度特性非常好。一般陶瓷金属封装的电路,工作温度为-55~+125℃;塑料封装的电路工作温度范围为-45~+85℃。

1.7扇出能力强扇出能力是用电路输出端所能带动的输入端数来表示的。由于CMOS集成电路的输入阻抗极高,因此电路的输出能力受输入电容的限制,但是,当CMOS集成电路用来驱动同类型,如不考虑速度,一般可以驱动50个以上的输入端。

2CMOS集成电路电阻的应用

2.1多晶硅电阻集成电路中的单片电阻器距离理想电阻都比较远,在标准的MOS工艺中,最理想的无源电阻器是多晶硅条。

式中:ρ为电阻率;t为薄板厚度;R□=(ρ/t)为薄层电阻率,单位为Ω/□;L/W为长宽比。由于常用的薄层电阻很小,通常多晶硅最大的电阻率为100Ω/□,而设计规则又确定了多晶硅条宽度的最小值,因此高值的电阻需要很大的尺寸,由于芯片面积的限制,实际上是很难实现的。当然也可以用扩散条来做薄层电阻,但是由于工艺的不稳定性,通常很容易受温度和电压的影响,很难精确控制其绝对数值。寄生效果也十分明显。无论多晶硅还是扩散层,他们的电阻的变化范围都很大,与注入材料中的杂质浓度有关。不容易计算准确值。由于上述原因,在集成电路中经常使用有源电阻器。

2MOS管电阻

MOS管为三端器件,适当连接这三个端,MOS管就变成两端的有源电阻。这种电阻器主要原理是利用晶体管在一定偏置下的等效电阻。可以代替多晶硅或扩散电阻,以提供直流电压降,或在小范围内呈线性的小信号交流电阻。在大多数的情况下,获得小信号电阻所需要的面积比直线性重要得多。一个MOS器件就是一个模拟电阻,与等价的多晶硅或跨三电阻相比,其尺寸要小得多。简单地把n沟道或p沟道增强性MOS管的栅极接到漏极上就得到了类似MOS晶体管的有源电阻。对于n沟道器件,应该尽可能地把源极接到最负的电源电压上,这样可以消除衬底的影响。同样p沟道器件源极应该接到最正的电源电压上。此时,VGS=VDS,如图1(a),(b)所示。图1(a)的MOS晶体管偏置在线性区工作,图2所示为有源电阻跨导曲线ID-VGS的大信号特性。这一曲线对n沟道、p沟道增强型器件都适用。可以看出,电阻为非线性的。但是在实际中,由于信号摆动的幅度很小,所以实际上这种电阻可以很好地工作。其中:K′=μ0C0X。可以看出,如果VDS(VGS-VT),则ID与VDS之间关系为直线性(假定VGS与VDS无关,由此产生一个等效电阻R=KL/W,K=1/[μ0C0X(VGS-VT)],μ0为载流子的表面迁移率,C0X为栅沟电容密度;K值通常在1000~3000Ω/□。实验证明,在VDS0.5(VGS-VT)时,近似情况是十分良好的。图1(c),(d)虽然可以改进电阻率的线性,但是牺牲了面积增加了复杂度。

在设计中有时要用到交流电阻,这时其直流电流应为零。图1所示的有源电阻不能满足此条件,因为这时要求其阻值为无穷大。显然这是不可能的。这时可以利用MOS管的开关特性来实现。

3电容电阻

交流电阻还可以采用开关和电容器来实现。经验表明,如果时钟频率足够高,开关和电容的组合就可以当作电阻来使用。其阻值取决于时钟频率和电容值。

在特定的条件下,按照采样系统理论,在周期内的变化可忽略不计。

其中,fc=1/T是信号Φ1和Φ2的频率。这种方法可以在面积很小的硅片上得到很大的电阻。例如,设电容器为多晶硅多晶硅型,时钟频率100kHz,要求实现1MΩ的电阻,求其面积。根据式(3)可知电容为10pF。假设单位面积的电容为0.2pF/mil2,则面积为50mil2。如果用多晶硅,取最大可能值100Ω,并取其最小宽度,那么需要900mil2。当然在开关电容电阻中除了电容面积外还需要两个面积极小的MOS管做开关。可以看出,电容电阻比多晶硅电阻的面积少了很多。而在集成电路设计中这是十分重要的。

有效的RC时间常数就与电容之比成正比,从而可以用电容和开关电容电阻准确的实现电路中要求的时间常数;而使用有源器件的电阻,可以使电阻尺寸最小。多晶硅电阻则是最简单的。在设计中要灵活运用这三种不同的方式。

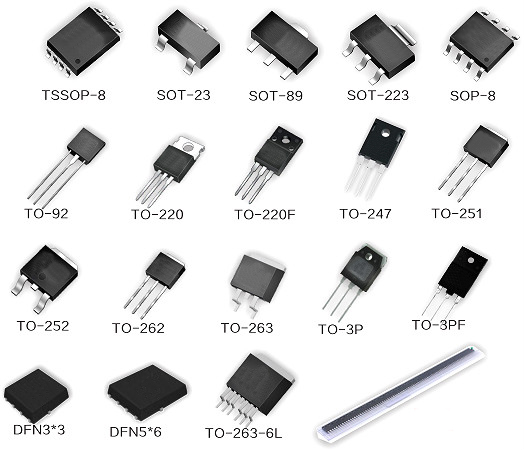

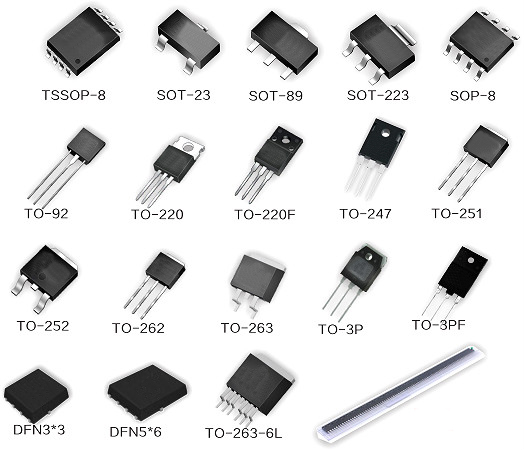

烜芯微专业制造二极管,三极管,MOS管,桥堆等20年,工厂直销省20%,4000家电路电器生产企业选用,专业的工程师帮您稳定好每一批产品,如果您有遇到什么需要帮助解决的,可以点击右边的工程师,或者点击销售经理给您精准的报价以及产品介绍

烜芯微专业制造二极管,三极管,MOS管,桥堆等20年,工厂直销省20%,4000家电路电器生产企业选用,专业的工程师帮您稳定好每一批产品,如果您有遇到什么需要帮助解决的,可以点击右边的工程师,或者点击销售经理给您精准的报价以及产品介绍