目前,MOSFET是ULSI电路中最主要的器件,由于它可比其他品种器件减少至更小的尺寸. MOSFET的主要技术为CMOS(CMOSFET,complementary MOSFET)技术,用此技术,n沟道与p沟道MOSFET(分别称为NMOS与PMOS)能够制造在同一芯片内.CMOS技术对ULSI电路而言特别具有吸收力,由于在一切IC技术中,CMOS技术具有最低的功率耗费.

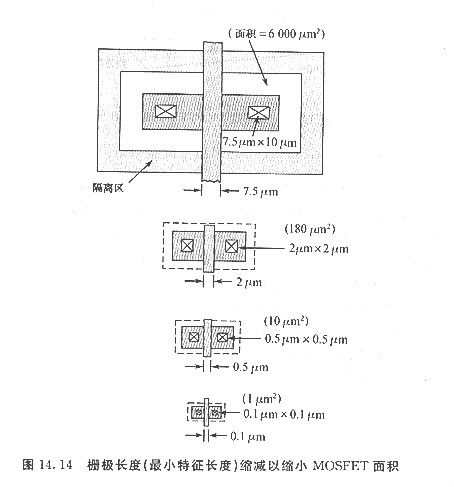

图14. 14显现近年来MOSFET的尺寸按比例减少的趋向.在20世纪70年代初期,栅极长度为7.5/μm其对应的器件面积大约为6000/μm2随着器件的减少,器件面积也大幅度地减少.关于一个栅极长度为o.5J‘m的MOSFET而言,器件面积能够减少至小于早MOSFET面积的1%.预期器件的减少化将会持续下去.在21世纪初,栅极长度将会小于o.10μm.我们将在14.5节讨论器件的将来趋向.

基本工艺

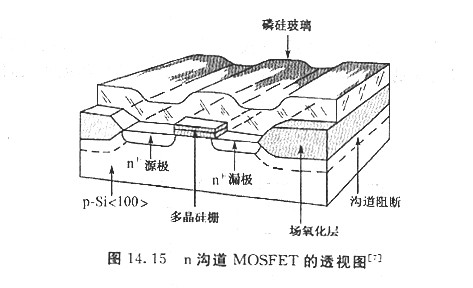

图14. 15显现一个尚未停止最后金属化工艺的n沟道MOS的透视图.最上层为磷硅玻璃(掺杂磷的二氧化硅,P-glass),它通常用来作为多晶硅栅极与金属连线间的绝缘体及町动离子的吸杂层( gettering layer).将图14. 15与表示双极型晶体管的图14.7作比拟,可留意到在根本构造方面MOSFET较为简单.固然这两种器件都运用横向氧化层隔离,但MOSFFET不需求垂直隔离,而双极型晶体管则需求一个埋层n+-p结.MOSFET的掺杂散布不像双极型晶体管那般复杂,所以掺杂散布的控制也就不那么重要.我们将讨论用来制造如图14. 15所示器件的主要工艺步骤.

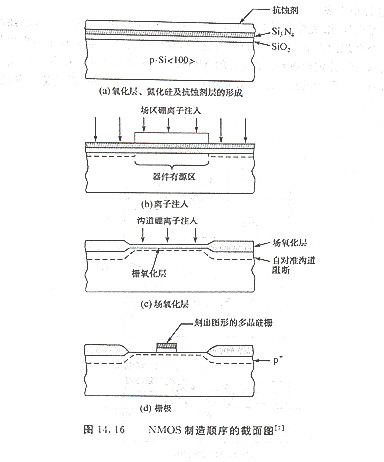

第一步制造一个n沟道MOSFET( NMOS),其起始资料为p型、轻掺杂(约1015cm-3)晶向、抛光的硅晶片.<100>品向的晶片<111>晶向的晶片好,由于其界面圈套密度(interface trap density)大约是<111>晶向上的非常之.第—步工艺是应用LOCOS技术构成氧化层隔离.这道工艺步骤与双极型晶体管工艺相似,都是先长一层薄的热氧化层作为垫层(约35nm),接着淀积氮化硅(约150 nm)[图14.16(a).有源器件区域是应用抗蚀剂作为掩蔽层定义出的,然后经过氮化硅—氧化层的组合物停止硼离子沟道阻断注入[图14,16(b)]).接着,刻蚀未被抗蚀剂掩盖的氮化硅层,在剥除抗蚀剂之后,将晶片置入氧化炉管,在氮化硅被去除掉的区域长一氧化层(称为场氧化层,field oxide),同时也注入硼离子,场氧化层的厚度通常为o.5μm一1μm.

第二步是生长栅极氧化层及调整阈值电压(threshold voltage)(参考6.2.3节),先去除在有源器件区域上的氮化硅—二氧化硅的组合物,然后长一层薄的栅极氧化层(小于10nm).如图14. 16(c)所示,对一个加强型n沟道的器件而言,注入硼离子到沟道区域来增加阈值电压至一个预定的值(如+o.5V).关于一个耗尽型n沟道器件而言,注入砷离子到沟道区域用以降低阈值电压(如-o.5 V).

第三步是构成栅极,先淀积一层多晶硅,再用磷的扩散或是离子注入,将多晶硅变为高浓度掺杂,使其薄层电阻到达典型的20Ω/口一30Ω/口,这样的阻值关于栅极长度大于3μm的MOSFET而言是恰当的,但是关于更小尺寸的器件而言,多晶硅化物( polycide)可用来当作栅极资料以降低薄层电阻至l.Ω/口左右,多晶硅化物为金属硅化物与多晶硅的组合物,常见的有钨的多晶硅化物(Wpolycide).

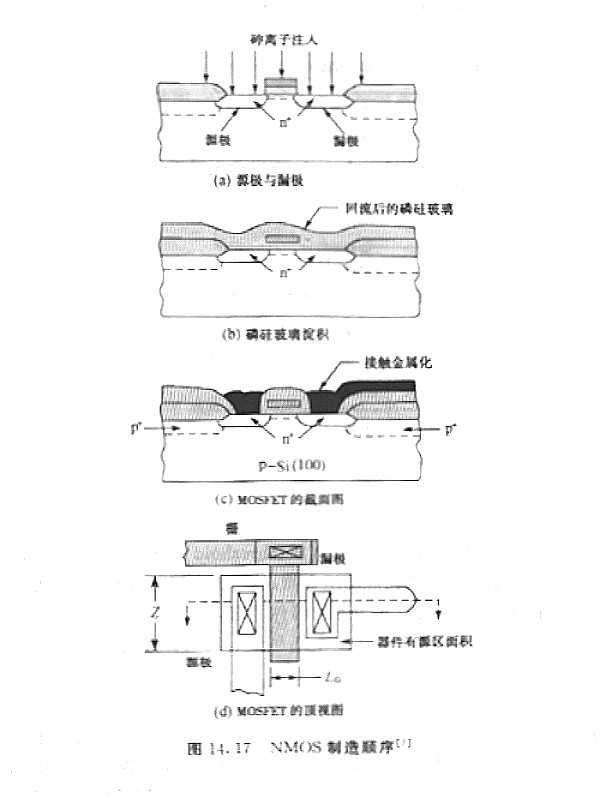

第四步是构成源极与漏极,在栅极图形完成后[图14. 16(d),栅极可用作砷离子注入(约30keV,约5×1015m—。)构成源极与漏极时的掩蔽层[图14. 17(a),因而源极与漏极对栅极而言也具有自对准的效果,所以独一形成栅极—漏极堆叠( overlap)的要素是由于注入离子的横向分布(lateral straggling)(关于30keV的砷,只要5nm).假如在后续工艺步骤中运用低温工艺将横向扩散降至最低,则寄生栅极-漏极电容与栅极—源极耦合电容将可比栅极—沟道电容小很多.

最后一步是金属化.先淀积磷硅玻璃(P-glass)于整片晶片上,接着经过加热晶片,使其活动以产生一个平整的外表[图14.17(b)].之后,在磷硅玻璃上定义和刻蚀出接触窗,然后淀积一金属层(如铝)并定出图形.完成后的MOSFET其截面如图14. 17(c)所示.图14.17(d)为对应的顶视图,栅极的接触通常被安顿在有源器件区域之外,以防止对薄栅极氧化层产生可能的伤害.

烜芯微专业制造二极管,三极管,MOS管,桥堆等20年,工厂直销省20%,1500家电路电器生产企业选用,专业的工程师帮您稳定好每一批产品,如果您有遇到什么需要帮助解决的,可以点击右边的工程师,或者点击销售经理给您精准的报价以及产品介绍