cmos应用

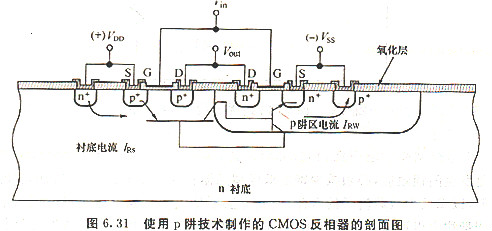

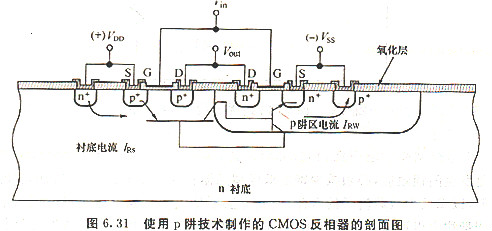

在CMOS应用中能同时将p沟道mos管与n沟道MOSFET制作在同一片芯片上.需要额外的掺杂及扩散步骤,以便在衬底中成“阱”或“盆(tub)”.阱中的掺杂种类与周围衬底不同.阱的典型种类有p阱、n阱以及双阱.阱技术的详细内容将于第14章中讨论.图6. 31为使用p阱技术制作的CMOS反相器的剖面图.在此图中,p沟道与n沟道MoSFET分别制作于n型硅衬底以及p阱之中.

cmos电路

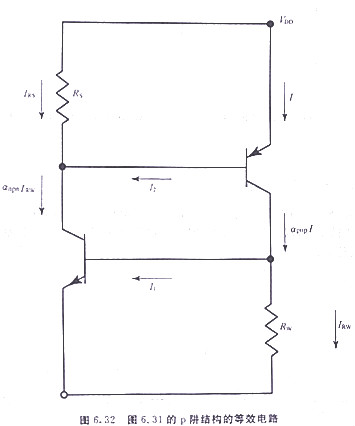

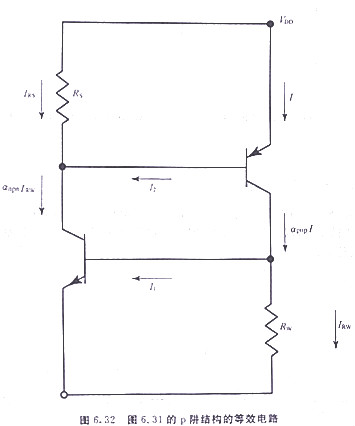

CMOS电路的阱结构最主要的问题在于闩锁现象,闩锁是由阱结构中寄生的pn—p-n二极管作用所造成的,如图6.3】所示,寄生的p—n-I,一n二极管是由一横向的p-n-p及一纵向的n-p-n双极型晶体管所组成的.p沟道MOSFFT的源极、n衬底及p阱分别为横向p-n-p双极型晶体管的发射极、基极及集电极;n沟道MOSFET的源极、p阱及n衬底分别为纵向n-p-n双极型晶体管的发射极、基极及集极其寄生部分的等效电路如图6.32所示.凡及Rw分别为衬底及阱中的串联电阻.每一晶体管的基极是由另一晶体管的集电极所MOS管驱动,并形成一正反馈回路,其架构就如第5章中所讨论的可控硅器件( thyristor).闩锁发生于两个双极型晶体管的共射电流增益乘积大于l时.当发生闩锁时'一大电流将由电源供应处(Vpo)流向接地端,导致一般正常电路工作中断,甚至会由于高电流散热的问题.而损坏芯片本身.

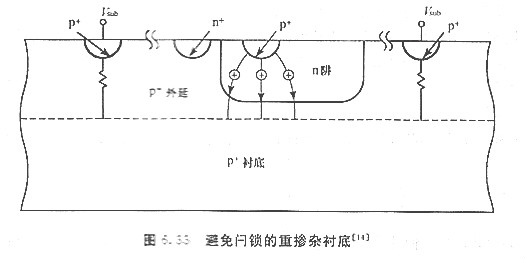

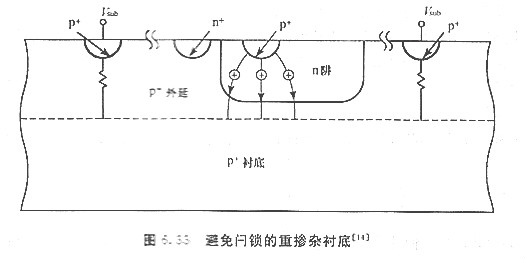

为避免发生闩锁效应,必须减少寄生双极型晶体管的电流增益,一种方法是使用金掺杂或中子辐射,以降低少数载流子的寿命,但此方法不易控制且也会导致漏电流的增加.深阱结构或高能量注入以形成倒退阱( retrograde well),可以提升基极杂质浓度,因而降低纵向双极型晶体管的电流增益.在倒退阱结构中,阱掺杂浓度的峰值位于远离表面的衬底中.另一种减少闩锁效应的方法,是将器件制作于高掺杂衬底上的低掺杂外延层中,如图6. 33所示.高掺杂衬底提供一个收集电流的高传导路径,这些电流随后会由表面接点流出.

闩锁亦可通过沟槽隔离(trench isolation.或译沟渠绝缘)结构来加以避开,制作沟槽隔离的工艺将于第14章中讨论.因为n沟道与p沟道MOSFET被沟槽所隔开,所以此种方法可以消除闩锁.

烜芯微专业制造二极管,三极管,MOS管,桥堆20年,工厂直销省20%,1500家电路电器生产企业选用,专业的工程师帮您稳定好每一批产品,如果您有遇到什么需要帮助解决的,可以点击右边的工程师,或者点击销售经理给您精准的报价以及产品介绍

烜芯微专业制造二极管,三极管,MOS管,桥堆20年,工厂直销省20%,1500家电路电器生产企业选用,专业的工程师帮您稳定好每一批产品,如果您有遇到什么需要帮助解决的,可以点击右边的工程师,或者点击销售经理给您精准的报价以及产品介绍