电阻简介

电阻(Resistance,通常用“R”表示),是一个物理量,在物理学中表示导体对电流阻碍作用的大小。导体的电阻越大,表示导体对电流的阻碍作用越大。不同的导体,电阻一般不同,电阻是导体本身的一种特性。电阻将会导致电子流通量的变化,电阻越小,电子流通量越大,反之亦然。而超导体则没有电阻。

电阻的本质与单位表示

(一)本质

正常金属有电阻,是因为载流子会受到散射而改变动量。散射的中心就是声子,缺陷,杂质原子等。在超导情况下,组成库伯对的电子不断地相互散射,但这种散射不影响库伯对质心动量,所以有电流通过超导体时库伯对的定向移动不受阻碍,没有电阻。

(二)单位表示

导体的电阻通常用字母R表示,电阻的单位是欧姆(ohm),简称欧,符号是Ω(希腊字母,读作Omega),1Ω=1V/A。比较大的单位有千欧(kΩ)、兆欧(MΩ)(兆=百万,即100万)。

KΩ(千欧), MΩ(兆欧),他们的换算关系是:两个电阻并联式也可表示为:1TΩ=1000GΩ;1GΩ=1000MΩ;1MΩ=1000KΩ;1KΩ=1000Ω(也就是一千进率)

功率MOSFET的导通电阻详解

电阻值的测量通常比较简单。但是,对于非常小阻值的测量,我们必须谨慎对待我们所做的假定。对于特定的几何形状,如电线,Kelvin方法是非常精确的。可以使用类似的方法来测量均匀样本的体电阻率和面电阻率,但是所使用的公式不同。在这些情况下,必须考虑探针间距和样本厚度。仅仅运用Kelvin法本身无法保证精度。如果布局和连接数发生变化,就很难精确地预测非均匀几何形状的电阻。

MOSFET最重要的特性之一就是漏极到源极的导通电阻(RDS(on))。在封装完成之后测量RDS(on)很简单,但是以晶圆形式测量该值更具有其优势。

(一)功率MOSFET的导通电阻-晶圆级测量

为了保证Kelvin阻值测量的精度,需要考虑几项重要的因素:(1)待测器件(DUT)的几何形状;(2)到器件的接线;(3)材料的边界;(4)各种材料(包括接线)的体电阻率。

一种测量RDS(on)的典型方法是在卡盘(Chuck)和接触晶圆顶部的探针之间产生电流。另一种方法是在晶圆的背面使用探针来代替卡盘。这种方法可以精确到2.5mΩ。

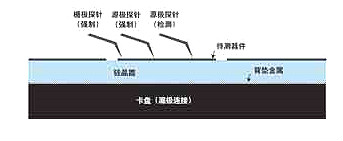

一种较大的误差来源于晶圆和卡盘之间的接触(如图1所示)。因为卡盘上以及晶圆背面粗糙不平,所以只有在个别点进行电气连接。晶圆和卡盘之间的接触电阻的数值足以给RDS(on)的测量引入较大的误差。仅仅重新放置卡盘上晶圆的位置就会改变接触区域并影响RDS(on)的测量结果。

图1 典型的测量结构,横截面视图

另一种测量偏差来源是探针的布局。如果移动了强制电流探针,电流的分布模式将发生变化。这会改变电压梯度模式,而且会改变电压检测探针处的电压。

(二)功率MOSFET的导通电阻-相邻晶粒方法

需要的设备包括:(1)带有6个可用探针的探针台;(2)电压计;(3)电流源。将晶圆和导电的卡盘隔离开这一点非常重要。如果晶圆与卡盘存在接触,那么这种接触将造成电流以平行于基底的方式流动,改变了测量结果。可以用一张纸将晶圆和卡盘隔离开。

到漏极的连接是通过在待测器件的另一侧使用相邻的完全相同的器件来实现的。内部晶圆结构要比晶圆和卡盘之间的连接牢固得多。因此,相邻晶粒方法要比传统的RDS(on)测量方法精确得多。

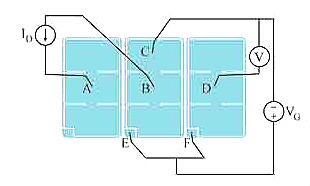

图2显示了测量的结构。3个MOSFET和6个探针均在图中显示出来,电接触则示意性地画出。中间的MOSFET是待测器件。

图2 RDS(on)测量结构

显示的极性属于N沟道MOSFET。漏极电流受限于探针的电流传输能力。左侧的MOSFET的作用是在待测器件的漏极侧施加电流。待测器件右侧的MOSFET用于测量漏极电压。

在MOSFET中,如果栅极开启,而且漏极到源极之间没有电流,那么漏极和源极的电压相等。这种方法就利用这个原理来测量探针D上的漏极电压。

栅极偏压被连接在探针C和E之间。如果连接在探针B和E之间,那么探针B和源极焊盘之间的电压降会降低待测器件上的实际栅极电压。因为在RDS(on)测量过程中没有电流通过,所以探针C上不存在电压降。

相邻晶粒方法确实需要右侧的MOSFET(在探针D和F之间)处于工作状态。如果这个晶粒上的栅极和源极被短路,那么测量结果可能不正确。

RDS(on)的取值是通过计算Vdc/IAB得到的,但是也可以得到更加精确的RDS(on)取值。

(三)功率MOSFET的导通电阻-FEA辅助确定RDS(on)测量值

尽管相邻晶粒法很精确,但是它并不能给出RDS(on)完全精确的测量值。为了得到仅由有源区贡献的RDS(on),可以将测量结果与仿真进行对比。有限元分析(FEA)软件可以用来为测量结构建模。一旦建立了有源区电阻和RDS(on)测量值之间的关系,就可以根据测量结果确定有源区的电阻。

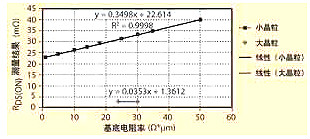

仿真模型是3个MOSFET和晶圆的一部分的三维表示。在有限元模型中,有源区电阻是已知的。FEA软件用来对测试结构建模并计算RDS(on)测量结果。仿真过程进行两次,使用两个不同的有源区电阻值来计算结果。因为响应的线性相当好,所以电阻值是任意选取的。对每种晶粒的尺寸,这种仿真只需要进行一次。利用仿真测量结果和实际有源区的电阻之间的关系,可以得到一个公式,用来根据相邻晶粒方法的测量值计算有源区电阻。

(四)功率MOSFET的导通电阻-相邻晶粒方法2

有几项因素会给测量引入误差。最重要的因素是探针的位置以及基底的电阻率。

从仿真结果可以看出,有些因素对测量结果的影响非常小。基底的厚度通常是200μm。厚度从175μm变化到225μm只会给RDS(on)带来1%的误差(仿真的测量结果)。同样,背垫金属表面电阻的变化对结果的影响也不会超过1%。仿真得到的一项惊人的结果表明,顶部金属厚度和电阻率对结果的影响也可以忽略不计。

基底电阻率的变化会给RDS(on)测量结果带来线性响应。图3显示了远远超出实际基底正常分布的基底电阻率。这样做是为了显示响应是线性的。

图3 由于基底电阻率造成的仿真结果的误差

探针在待测器件上的摆放位置必须保持一致。探针位置的变化会造成测量结果的变化。待测器件左侧和右侧器件上探针的位置(见图2中的A和D)也会影响测量结果,但是影响没有前者大。造成这种测量误差的原因在于顶部金属的表面电阻大于0。

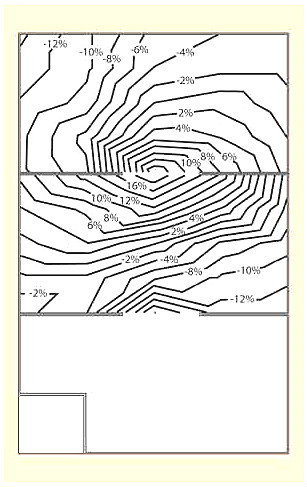

将探针B或C从源极焊盘中心向边缘移动会导致较大的误差。图4显示了移动探针B或C所产生的误差。每条线表示RDS(on) 2%的误差。在绘制这张图时,使用了5μm×5μm的网格。每次只移动一个探针的位置。

图4 探针位置所引起的误差

相邻晶粒方法是一种成本低廉、精确地以晶圆形式测量MOSFET有源区的RDS(on)的方法。它在检测不同批次晶圆的差别方面非常有用。

MOSFET的导通电阻的作用

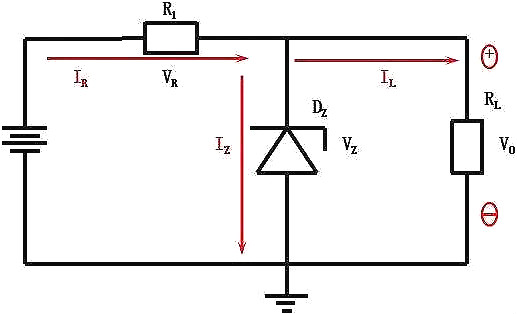

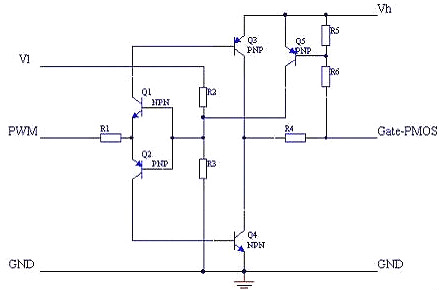

mos管导通电阻,一般在使用MOS时都会遇到栅极的电阻选择和使用问题,但有时对这个电阻很迷茫,现介绍一下它的作用:

1.是分压作用

2.下拉电阻是尽快泄放栅极电荷将MOS管尽快截止

3.防止栅极出现浪涌过压(栅极上并联的稳压管也是防止过压产生)

4.全桥栅极电阻也是同样机理,尽快泄放栅极电荷,将MOS管尽快截止。避免栅极悬空,悬空的栅极MOS管将会导通,导致全桥短路

5.驱动管和栅极之间的电阻起到隔离、防止寄生振荡的作用

降低高压MOSFET的导通电阻的原理与方法

1.不同耐压的MOS管的导通电阻分布。不同耐压的MOS管,其导通电阻中各部分电阻比例分布也不同。如耐压30V的MOS管,其外延层电阻仅为总导通电阻的29%,耐压600V的MOS管的外延层电阻则是总导通电阻的96.5%。

由此可以推断耐压800V的MOS管的导通电阻将几乎被外延层电阻占据。欲获得高阻断电压,就必须采用高电阻率的外延层,并增厚。这就是常规高压MOS管结构所导致的高导通电阻的根本原因。

2.降低高压MOS管导通电阻的思路。增加管芯面积虽能降低导通电阻,但成本的提高所付出的代价是商业品所不允许的。引入少数载流以上两种办法不能降低高压MOS管的导通电阻,所剩的思路就是如何将阻断高电压的低掺杂、高电阻率区域和导电通道的高掺杂、低电阻率分开解决。如除导通时低掺杂的高耐压外延层对导通电阻只能起增大作用外并无其他用途。

这样,是否可以将导电通道以高掺杂较低电阻率实现,而在MOS管关断时,设法使这个通道以某种方式夹断,使整个器件耐压仅取决于低掺杂的N-外延层。基于这种思想,1988年INFINEON推出内建横向电场耐压为600V的COOLMOS管,使这一想法得以实现。内建横向电场的高压MOS管的剖面结构及高阻断电压低导通电阻的示意图如图所示。

与常规MOS管结构不同,内建横向电场的MOS管嵌入垂直P区将垂直导电区域的N区夹在中间,使MOS管关断时,垂直的P与N之间建立横向电场,并且垂直导电区域的N掺杂浓度高于其外延区N-的掺杂浓度。

当VGS<VTH时,由于被电场反型而产生的N型导电沟道不能形成,并且D,S间加正电压,使MOS管内部PN结反偏形成耗尽层,并将垂直导电的N区耗尽。这个耗尽层具有纵向高阻断电压,如图(b)所示,这时器件的耐压取决于P与N-的耐压。因此N-的低掺杂、高电阻率是必需的。

烜芯微专业制造二极管,三极管,MOS管,20年,工厂直销省20%,1500家电路电器生产企业选用,专业的工程师帮您稳定好每一批产品,如果您有遇到什么需要帮助解决的,可以点击右边的工程师,或者点击销售经理给您精准的报价以及产品介绍