1.NMOS+PMOS-构成CMOS

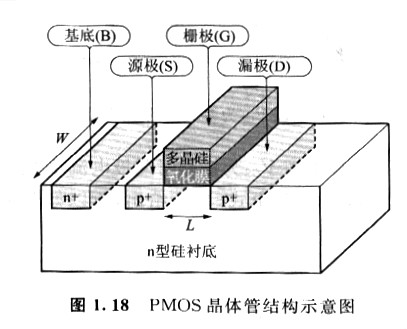

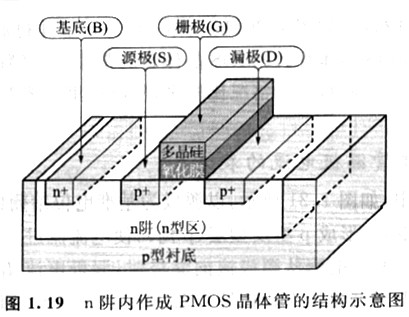

图1. 18所示的PMOS晶体管是在n型基底上构成p+型的源区和漏区。假如采用p型硅衬底,如图1.19所示,在p型衬底上先作成n型基底,把这个n型区域称为n阱( well)。

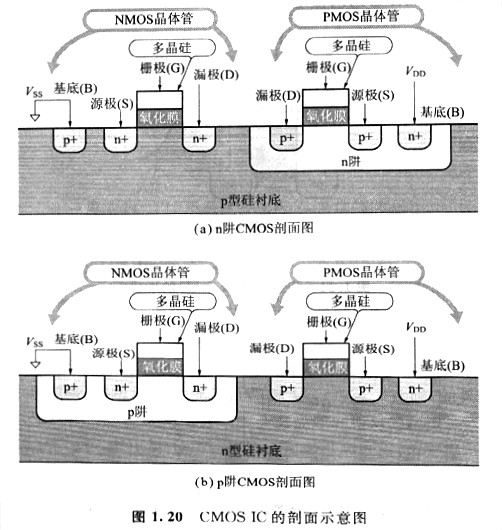

图1. 20(a)是在p型硅衬底上构成的CMOS剖面表示图。以n阱为基底作成PMOS晶体管,以p型硅衬底为基底作成NMOS晶体管。

通常n阱中需介入n+区与正电源电压VDD衔接,也有可能取独立的电位。例如,p型硅衬底上构成多个n阱时,也能够其中某一个n阱与VDD衔接,而其他n阱与源极取等电位。但是p型硅衬底必需与负电源电压衔接。就是说PMOS晶体管的基底可取的电位与NMOS晶体管相比,自在度要大。

假如运用n型硅衬底,如图1. 20(b)所示,先在n型硅衬底上构成p阱,作成以p阱为基底的NMOS晶体管。PMOS晶体管的基底是n型硅衬底。

普通来说,运用p型硅衬底的状况比拟多,所以这里主要对运用p型硅衬底的状况停止讨论。

2. PMOS晶体管漏极电流的表达式

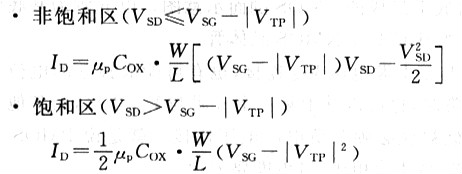

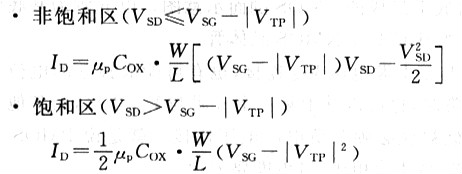

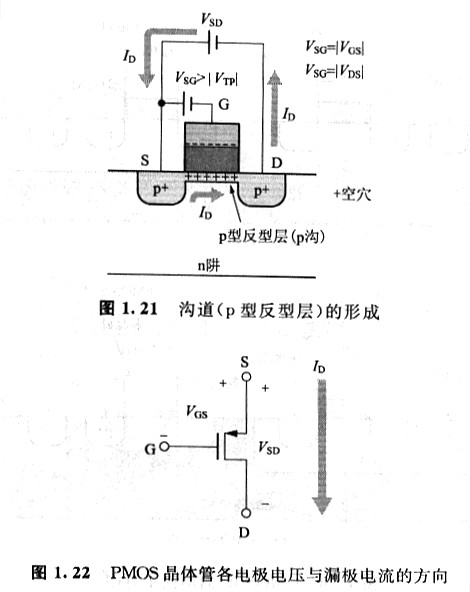

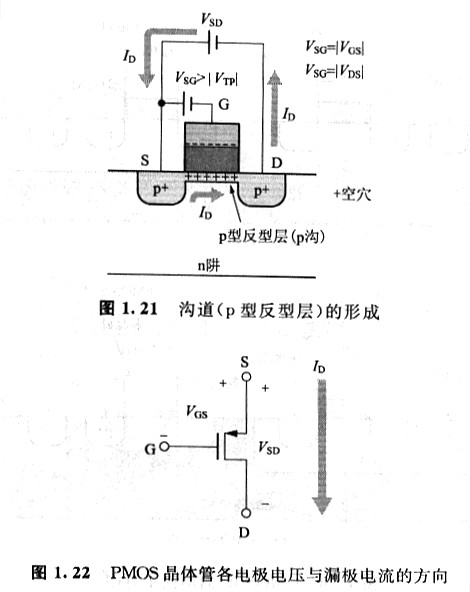

PMOS晶体管中,如图1.21所示,以源极为基准电位给栅极加负的电压,在栅氧化膜下方感应出空穴,构成p型反型层(p沟),使电流流过。所以PMOS晶体管的阈值电压VTP是负值。电流从源极流向漏极时,漏极电流ID取正值,源极—栅极间电压V SG和源极—漏极间电压VSD取图1,22所示的极性时,PMOS晶体管的漏极电流ID由下式给出:

式中,VTP是PMOS晶体管的阈值电压。

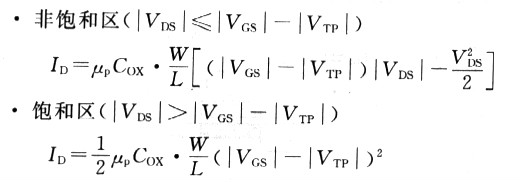

如果采用各电压的绝对值,那么漏极电流的式(1.1)和式(1.4)也分别适用NMOS晶体管和PMOS晶体管;

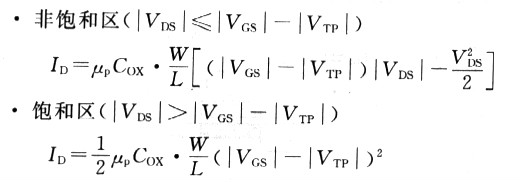

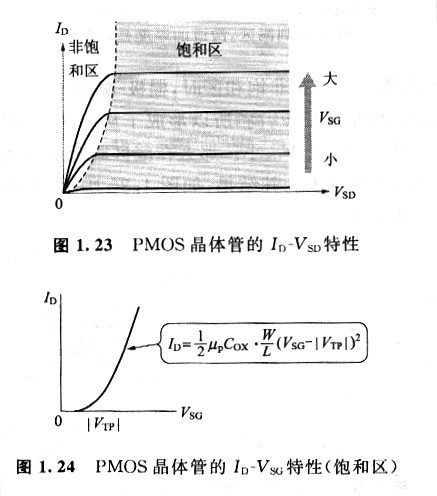

图1. 23和图1.24分别示出漏极电流与源极漏极间电压的关系曲线,以及漏极电流与源极—栅极间电压的关系曲线。

烜芯微专业制造二极管,三极管,MOS管,20年,工厂直销省20%,1500家电路电器生产企业选用,专业的工程师帮您稳定好每一批产品,如果您有遇到什么需要帮助解决的,可以点击右边的工程师,或者点击销售经理给您精准的报价以及产品介绍