当NMOS管的栅极与源极短接(即NMOS管的栅/源电压VGS=O)时,源区(N+型)、衬底(P型)和漏区(N+型)形成两个背靠背的PN结,不管NMOS管的漏/源电压VDS的极性如何,其中总有一个PN结是反偏的,所以NMOS管源极与漏极之间的电阻主要为PN结的反偏电阻,基本无电流流过,即NMOS管的漏极电流ID为0。例如,如果NMOS管的源极S与衬底相连,并接到系统的最低电位,而漏极接电源正极时,漏极和衬底之间的PN结是反偏的,此时漏、源之间的电阻很大,没有形成导电沟道

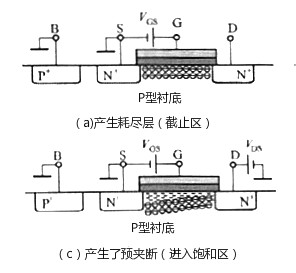

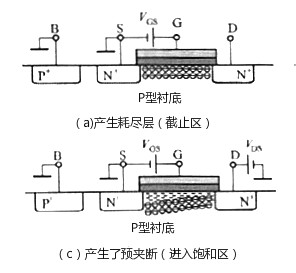

若在NMOS管的栅/源之间加上止向电压VGS(即NMOS管的栅极接高电位,源极接低电位),则栅极和P型衬底之间就形成了以栅氧(即二氧化硅)为介质的平板电容器。在正的栅源电压作用下,介质中产生了一个垂直于硅片表面的由栅极指向P型衬底的强电场(由于绝缘层很薄,即使只有儿伏的栅/源电压VGS,也可产生高达105~106V/cm数量级的强电场),这个强电场会排斥衬底表面的空穴而吸引电子,因此,使NMOS管栅极附近的P型衬底中的空穴被排斥,留下不能移动的受主离子(负离子),形成了耗尽层,同时P型衬底中的少子(电子)被吸引到衬底表面,如图1.3(a)所示。当正的栅/源电压达到一定数值时,这些电子在

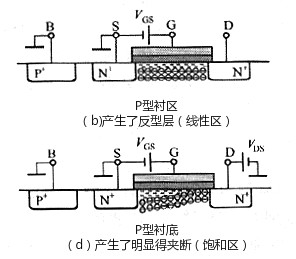

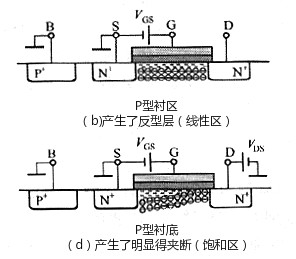

栅极附近的P型硅表面便形成了一个N型薄层,通常把这个在P型硅表面形成的N型薄层称为反型层,这个反型层实际上就构成了源极和漏极间的N型导电沟道,如图1.3(b)所示。

由于它是栅/源止电压感应产生的,所以也称感生沟道。显然,栅/源电压VGs止得越多,则作用于半导体表面的电场就越强,吸引到P型硅表面的电子就越多,感应沟道(反型层)将越厚,沟道电阻将越小。

感应沟道形成后,原来被P型衬底隔开的两个N+型区(源区和漏区)就通过感应沟道连接在一起。因此,在正的漏/源电压作用下,电子将从源区流向漏区,产生了漏极电流ID。一般把在漏源电压作用下开始导电时的栅/源电压叫做NMOS管的阈值电压(或开启电压)Vth。

当NMOS管的栅/源电压VGS大于等于Vth时,外加较小的漏/源电压VDS时,漏极电流ID将随VDS上升迅速增大,此时为线性区(也可称为三极管区),但由于沟道存在电位梯度,即NMOS管的栅极与沟道间的电位差从漏极到源极逐步增大,因此所形成的沟道厚度是不均匀的,靠近源端的沟道厚,而靠近漏端的沟道薄。

当VDS增大到一定数值,即VGD=Vth时,靠近漏端的沟道厚度接近为o,即感应沟道在漏端被夹断,如图1.3(c)所示:VDS继续增加,将形成一夹断区,且夹断点向源极靠近,如图1.3(d)所示。沟道被夹断后,VDS上升时,其增加的电压基本上加在沟道厚度为零的耗尽区上,而沟道两端的电压保持不变,所以ID于饱和而不再增加,此时NMOS管工作在饱和区,在模拟集成电路巾饱和区是NMOS管的主要工作区。要注意,此时沟道虽产生了灾断,但由于漏极与沟道之间存在强电场,电子在该电场作用下被吸收到漏区而形成了从源区到漏区的电流。

另外,当VGS增加时,由丁感应沟道变厚,沟道电阻减小,饱和漏极电流会相应增大。

若Vns人于某一击穿电压BVus(二极管的反向击穿电压),漏极与衬底之间的PN结发生反向击穿,ID将急剧增加,进入雪崩区,漏极电流不经过沟道,而直接由漏极流入衬底。

注意与双极型晶体管相比,一个MOS管只要形成了导,t1沟道,即使在无电流流过时也可以认为是开通的。

烜芯微专业制造二极管,三极管,MOS管,20年,工厂直销省20%,1500家电路电器生产企业选用,专业的工程师帮您稳定好每一批产品,如果您有遇到什么需要帮助解决的,可以点击右边的工程师,或者点击销售经理给您精准的报价以及产品介绍

烜芯微专业制造二极管,三极管,MOS管,20年,工厂直销省20%,1500家电路电器生产企业选用,专业的工程师帮您稳定好每一批产品,如果您有遇到什么需要帮助解决的,可以点击右边的工程师,或者点击销售经理给您精准的报价以及产品介绍