mos晶体管,金属-氧化物-半导体(Metal-Oxide-Semiconductor)结构的晶体管简称MOS晶体管,有MOS管构成的集成电路称为MOS集成电路。

MOS管晶体管开通过程

MOS晶体管,开关管的开关模式电路如图所示,二极管可是外接的或MOS管固有的。开关管在开通时的二极管电压、电流波形如图5所示。在图5的阶段1开关管关断,开关电流为零,此时二极管电流和电感电流相等;在阶段2开关导通,开关电流上升,同时二极管电流下降。开关电流上升的斜率和二极管电流下降的斜率的绝对值相同,符号相反;在阶段3开关电流继续上升,二极管电流继续下降,并且二极管电流符号改变,由正转到负;在阶段4,二极管从负的反向最大电流IRRM开始减小,它们斜率的绝对值相等;在阶段5开关管完全开通,二极管的反向恢复完成,开关管电流等于电感电流。

电介质在决定阈值电压方面也起了重要作用。厚电介质由于比较厚而削弱了电场。所以厚电介质使阈值电压上升,而薄电介质使阈值电压下降。理论上,电介质成分也会影响电场强度。而实际上,几乎所有的MOS管都用纯二氧化硅作为gate dielectric。这种物质可以以极纯的纯度和均匀性生长成非常薄的薄膜;其他物质跟它都不能相提并论。因此其他电介质物质只有很少的应用。(也有用高介电常数的物质比如氮化硅作为gate dielectric的器件。有些作者把所有的MOS类晶体管,包括非氧化物电介质,称为insulated-gate field effect transistor(IGFET))

gate的物质成分对阈值电压也有所影响。如上所述,当GATE和BACKGATE短接时,电场就出现在gate oxide上。这主要是因为GATE和BACKGATE物质之间的work function差值造成的。大多数实际应用的晶体管都用重掺杂的多晶硅作为gate极。改变多晶硅的掺杂程度就能控制它的work function。

GATE OXIDE或氧化物和硅表面之间界面上过剩的电荷也可能影响阈值电压。这些电荷中可能有离子化的杂质原子,捕获的载流子,或结构缺陷。电介质或它表面捕获的电荷会影响电场并进一步影响阈值电压。如果被捕获的电子随着时间,温度或偏置电压而变化,那么阈值电压也会跟着变化。

影响MOS晶体管的因素

第一个影响阈值电压的因素是作为介质的二氧化硅(栅氧化层)中的电荷Qss以及电荷的性质。这种电荷通常是由多种原因产生的,其中的一部分带正电,一部分带负电,其净电荷的极性显然会对衬底表面产生电荷感应,从而影响反型层的形成,或者是使器件耗尽,或者是阻碍反型层的形成。Qss通常为可动正电荷。

第二个影响阈值电压的因素是衬底的掺杂浓度。从前面的分析可知,要在衬底的上表面产生反型层,必须施加能够将表面耗尽并且形成衬底少数载流子的积累的栅源电压,这个电压的大小与衬底的掺杂浓度有直接的关系。衬底掺杂浓度(QB)越低,多数载流子的浓度也越低,使衬底表面耗尽和反型所需要的电压VGS越小。

所以,衬底掺杂浓度是一个重要的参数,衬底掺杂浓度越低,器件的阈值电压数值将越小,反之则阈值电压值越高。对于一个成熟稳定的工艺和器件基本结构,器件阈值电压的调整,主要通过改变衬底掺杂浓度或衬底表面掺杂浓度进行。衬底表面掺杂浓度的调整是通过离子注入杂质离子进行。

第三个影响阈值电压的因素是由栅氧化层厚度tOX决定的单位面积栅电容的大小。单位面积栅电容越大,电荷数量变化对VGS的变化越敏感,器件的阈值电压则越小。

实际的效应是,栅氧化层的厚度越薄,单位面积栅电容越大,相应的阈值电压数值越低。但因为栅氧化层越薄,氧化层中的场强越大,因此,栅氧化层的厚度受到氧化层击穿电压的限制。选用其他介质材料做栅介质是当前工艺中的一个方向。例如选用氮氧化硅 SiNxOy 替代二氧化硅是一个微电子技术的发展方向。正在研究其它具有高介电常数的材料,称为高k栅绝缘介质。

第四个对器件阈值电压具有重要影响的参数是栅材料与硅衬底的功函数差ΦMS的数值,这和栅材料性质以及衬底的掺杂类型有关,在一定的衬底掺杂条件下,栅极材料类型和栅极掺杂条件都将改变阈值电压。对于以多晶硅为栅极的器件,器件的阈值电压因多晶硅的掺杂类型以及掺杂浓度而发生变化。

可见,在正常条件下,很容易得到增强型PMOS管。为了制得增强型NMOS管,则需注意减少Qss、Qox,增加QB。采用硅栅工艺对制做增强型NMOS管和绝对值小的增强型PMOS管有利。

MOS晶体管低功耗电路

MOS晶体管功耗电路,应对器设计的本钱依赖于几个要素,而不只仅是硅的本钱。事实上,芯片制造工艺的本钱(就其复杂性和成熟水平与良率而言)普通能够由电路设计师来控制。依据经历,当裸片面积超越1mm2时,用于供给链应用的RFID的本钱开端降落。

当RFID应对器从系统的最小范围运动到最大范围时,其功率大致变化三十倍,所以RFID应对器的功率请求可能对设计师提出了一个难于预测的应战。虽然UHFRFID应对器能够取得的典型功率在一百毫瓦数量级,但该问题并非仅限于功耗。即便是在短间隔内,能够对应对器提供足够的功率却可能招致电压过载。应对器还必需工作在从-25℃~+40℃的标称工作范围内,以从-40℃~+65℃基于EPCGen2规范的扩展温度范围内。

本钱与功率请求极大地影响了对用于消费RFID应对器IC的工艺选择。正如在先前系列文章中所提到的,肖特基接触在RFID应对器设计中提供了低开启电压、低结电容以及高电流驱动。另外,曾经有人努力于采用新的工艺,例如BiCMOS以及蓝宝石硅片(SOS),其提供了极佳的低功耗性能。但每种办法都有其不利的一面。在CMOS工艺中肖特基接触并非是常规的,而普通需求后处置步骤。其它工艺诸如BiCMOS和SOS对大多数RFID应对器应用而言又太贵了。

MOS管晶体管功耗电路,完成低功耗电路请求的另一个办法是动态阈值电压MOSFET技术。其能够应用体硅CMOS技术完成低价消费。其全部优势十分合适于开发下一代UHFRFID应对器,本文将对此作细致阐述。本文将首先引见DTMOS的根本原理。接下来,DTMOS在数字、模仿以及射频范畴的完成将被重点阐明,这是由于UHFRFID应对器包括了触及一切这三个范畴的电路。最后,将演示满足EPCGen2指标UHFRFID的DTMOS带隙参考电路的芯片完成。

DTMOS属于根本上采用互连的阱和栅的MOS管晶体管(图1)。关于双阱p衬底CMOS工艺,由于只能单独控制和消费N阱的这一事实,所以只能采用P型DTMOS,这是由于N型DTMOS的P阱具有到P衬底的共同和低欧姆的通路。但是,N型DTMOS能够在具有深N阱特性的工艺中取得。DTMOS的操作相似于弱反型MOS的操作,类似于横向PNP管中的三极管操作。弱反型MOS晶体管的漏电流与横向PNP的集电极电流(都在饱和区)为:

其中:F=FBJT=VBE。用于三极管,F=FWIM=[(VGS-VT)×COX/(COX+Cdepletion)]

用于弱反型MOS晶体管。

耗尽层电容的值依赖于耗尽层的宽度,其依次依赖于阱的掺杂特性,以及在硅中源极结左近的电压降。因而,该要素依赖于所采用的阱-源电压和经过阈值调制效应所采用的阱-源电压。

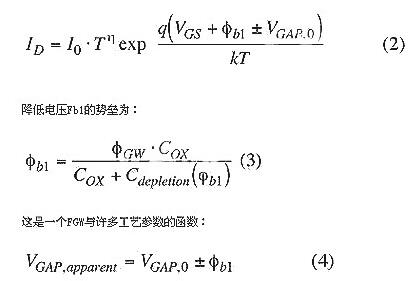

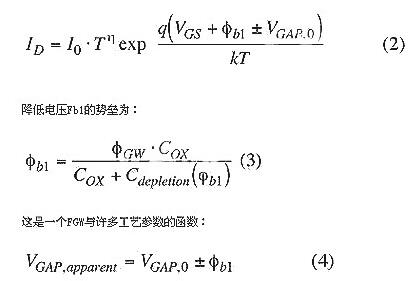

DTMOS能够被看作基极上具有额外栅的横向双极PNP管。基于这一观念,DTMOS的漏电流主要取决于经过源—阱结的电压,其在VGS与ID之间产生了理想的指数(相似双极)关系。由于互连栅—阱的存在,在栅和阱之间存在着内建电压FGW。由于电容的分配,电压FGW在栅氧和硅上被再次分配。这意味着硅中的电压降由于FGW作为势垒,降低了电压Fb1,DTMOS的漏电流能够表示为:

由这些推导得出的关键结果如下:

1.与硅PN结的1.2V相比,DTMOS器件的带隙显然是0.6V;

2.DTMOS器件具有理想的指数特性[IDaexp(qVGS/kT)];

3.DTMOS器件的横向电流具有exp(qFb1/kT)因子,其比通常的横向PNP要大;

4.带隙电压具有明显的温度依赖性。采用0.25umDTMOS工艺消费的初步胜利设计工作在77K温度下,运用0.6V电源电压并将衬底衔接到固定的正向偏置电压。接下来的实验包括受控栅横向双极晶体管以及衬底衔接到栅端的硅绝缘体(SOI)MOSFET工艺。第一种工艺用于小型的低功耗模仿应用,而第二种工艺是超低功耗CMOS的典型最佳候选技术。

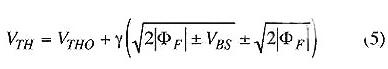

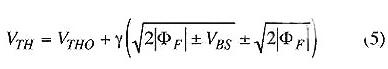

DTMOS技术在其产生的栅—延迟/功耗方面与传统的CMOS电路技术相比显现出惊人的性能优势。DTMOS还在RF电路中显现出优越性能。在传统的CMOS中,减少到更小特征尺寸和阈值电压(VTH)的工艺增加了工作速度。但是,VTH的降低也招致了亚阈值MOSFET行为的降落。静态电路中静态电流的增加,将VTH限制为0.4V。DTMOS可能能够克制这些约束,特别是工作在具有峻峭的亚阈值特性的极低VDD和低VTH下。对DTMOS,栅输入电压正向偏置了衬底,依据著名的体效应公式,VTH将降低:

烜芯微专业制造二三极管,MOS管,20年,工厂直销省20%,1500家电路电器生产企业选用,专业的工程师帮您稳定好每一批产品,如果您有遇到什么需要帮助解决的,可以点击右边的工程师,或者点击销售经理给您精准的报价以及产品介绍

烜芯微专业制造二三极管,MOS管,20年,工厂直销省20%,1500家电路电器生产企业选用,专业的工程师帮您稳定好每一批产品,如果您有遇到什么需要帮助解决的,可以点击右边的工程师,或者点击销售经理给您精准的报价以及产品介绍