当器件加有过大的电压或电流时,器件会遭到损伤而导致性能劣化,严重时会被击穿。这时芯片上的布线或器件的分离局部将会被毁坏,或者与上下/左右相邻的布线或器件短路,以至于信号线开路或短路。

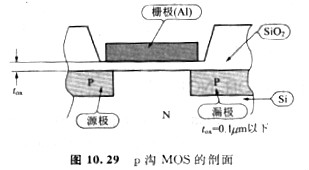

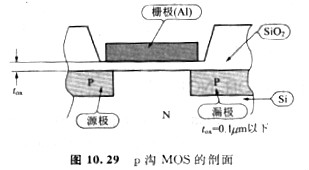

CMOS器件的输入连接在n沟晶体管或者p沟晶体管的栅极上。图10. 29示出MOS晶体管的剖面,栅区有一层十分薄的绝缘氧化膜(Si02)。Si02膜具有109V/m(103 V/μm)的绝缘强度。不过由于CMOS器件的栅氧化膜厚度在0.1μm以下,十分薄,一切几十伏至几百伏的电压就会惹起绝缘击穿。

人身体产生的静电会高达几千伏至几万伏,冬天用手触摸CMOS器件时,很容易损坏器件。为了免受静电对栅氧化膜形成损伤,在CMOS器件的输入局部都配置有维护电路。

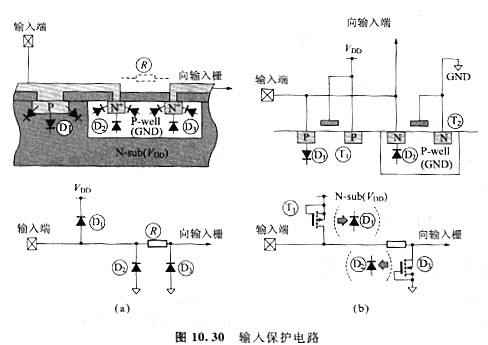

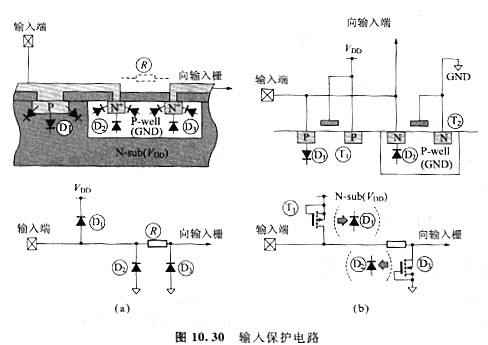

图10. 30示出典型的输入维护电路。在原来的等效电路中的输入信号线上附加二极管,起到维护电路的作用。当输入端由于静电等缘由加有过大的电压/电流时,它能够使正电荷沿电源线,负电荷沿GND线逃逸。

图10. 30(a)的维护电路设置有扩散电阻,关于二极管短时间内吸收不了的能量,它起到延迟电路的作用,延缓这些能量向栅极传送。它的弊端是在高速CMOSIC中会招致信号传输时间的滞后。

图10. 30(b)的维护电路运用了等效构成二极管的MOS晶体管。用这个电路,能够使MOS晶体管ON时电荷经过沟道逃逸。依照普通的二极管方式,作为维护电路有良好的响应性,不过从芯片面积以及幅员设计角度看,有不利影响。

输出的维护

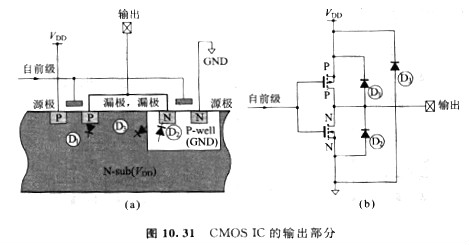

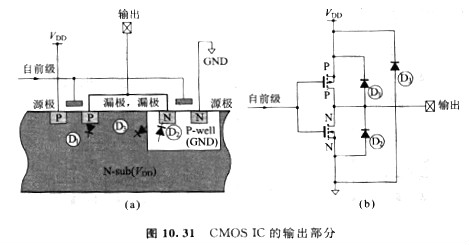

图10. 31示比CMOS IC的输出局部。输出n沟晶体管/p沟晶体管的漏极相互衔接构成输出端。在漏极局部各自构成寄生的pn二极管/np二极管。由于这些二极管,能够维护输出局部的过大电压。另外,在某些情况下也能使输出晶体管内身瞬态ON,免受异常电荷的损害。

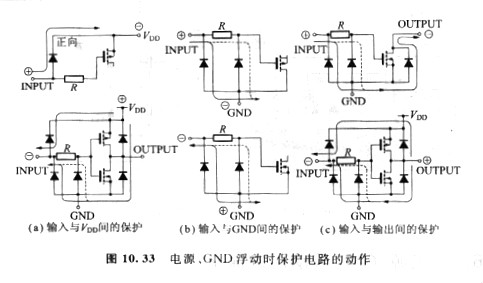

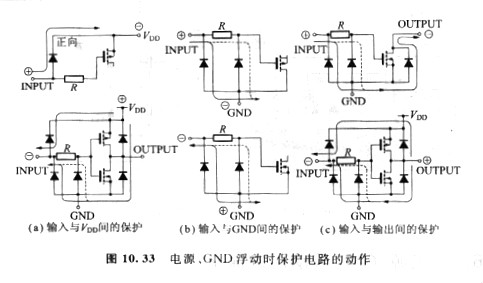

电源/GND浮动时的维护

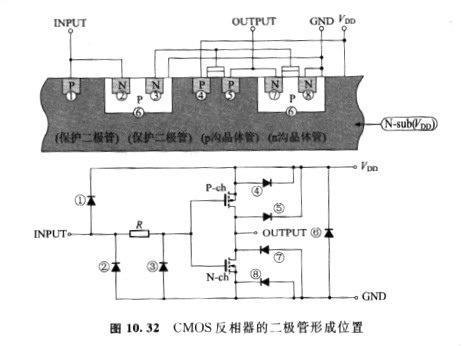

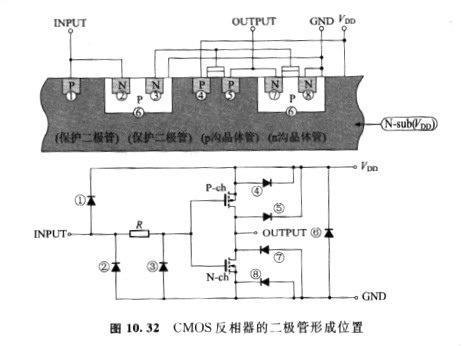

当CMOS器件没有装置在印制电路板上,而是处于单个焊接状态时,假如呈现异常的外加电压,该如何处置呢?VDD或GND会有浮动的状况,怎样维护呢?图10.32示出CMOS器件的最小电路构造反相器电路以及输入维护电路的例子。

CMOS IC由于插入输入维护电路,一切的端子都用二极管与电源VDD或者GND衔接。当输入端与VDD GND之间有异常电压时,如图10. 33所示,必然形成正向或者反向流入二极管的电流通道,维护内部电路。这就是说,假如二极管的反向耐压比MOS晶体管的栅氧化膜的绝缘击穿电压低,那么关于装置前的异常电压就具有维护电路的作用。

烜芯微专业制造二三极管,MOS管,20年,工厂直销省20%,1500家电路电器生产企业选用,专业的工程师帮您稳定好每一批产品,如果您有遇到什么需要帮助解决的,可以点击右边的工程师,或者点击销售经理给您精准的报价以及产品介绍

烜芯微专业制造二三极管,MOS管,20年,工厂直销省20%,1500家电路电器生产企业选用,专业的工程师帮您稳定好每一批产品,如果您有遇到什么需要帮助解决的,可以点击右边的工程师,或者点击销售经理给您精准的报价以及产品介绍